Cavium Processor Complex: StratixGX Interconnect

ATCA-9305 User’s Manual 10009109-01

3-10

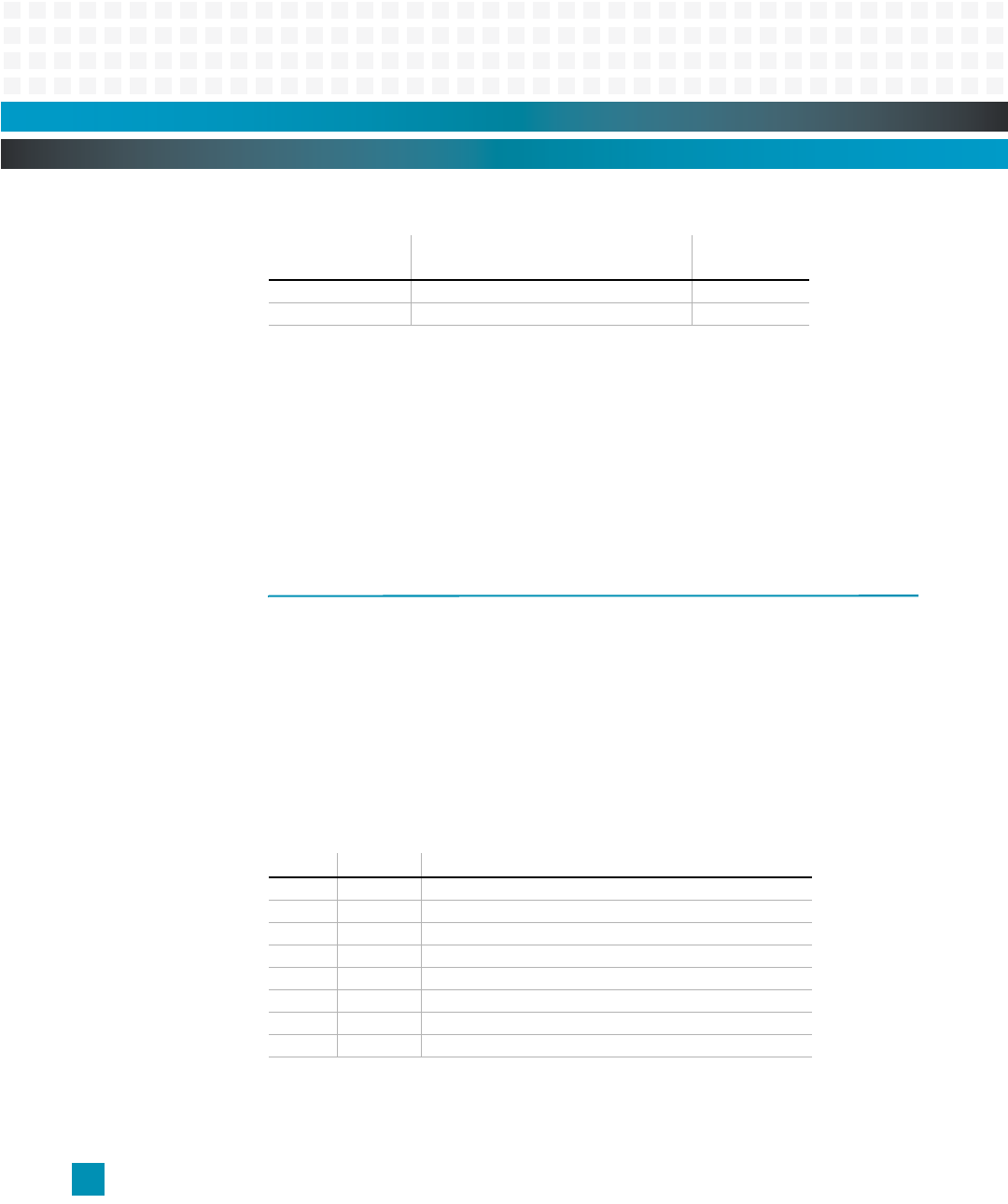

Table 3-6: Cavium NVRAM Memory Map

Flash, 512 KB x 8

The 512 KB of 32-pin PLCC socketed flash starts at physical address1D46,0000

16

and is used

for Engineering code.

The StrataFlash features high-performance fast asynchronous access

times, low power, and flexible security options.

Flash, 4 MB x 16

The 4 MB soldered NOR flash starts at physical address 1D05,0000

16.

The 32-Mbit device

provides CN5860 code storage and non-volatile memory.

STRATIXGX INTERCONNECT

The Altera StratixGX FPGA provides the high-speed SPI-4.2 interconnect. Each complex has

dual SPI-to-XAUI bridges connected to the XAUI Ethernet switch ports.

PLD Registers

The FPGA bridge is located at address 0x1D030000. Use the following registers to access

the XAUI to SPI bridge configuration registers. See the “Read Example” and “Write Exam-

ple.”

Data Registers

Register 3-1: Data 31:24 (0x0)

Address Offset

(hex): Description:

Window

Size (bytes)

0x1E00-0x1FFF Monitor parameters 256

0x0000-0x1D36 User defined 79F

Bits: R/W: Function:

7R/WData 31

6R/WData 30

5R/WData 29

4R/WData 28

3R/WData 27

2R/WData 26

1R/WData 25

0R/WData 24