Management Processor CPLD: MPC8548 PLD Register

10009109-01 ATCA-9305 User’s Manual

5-13

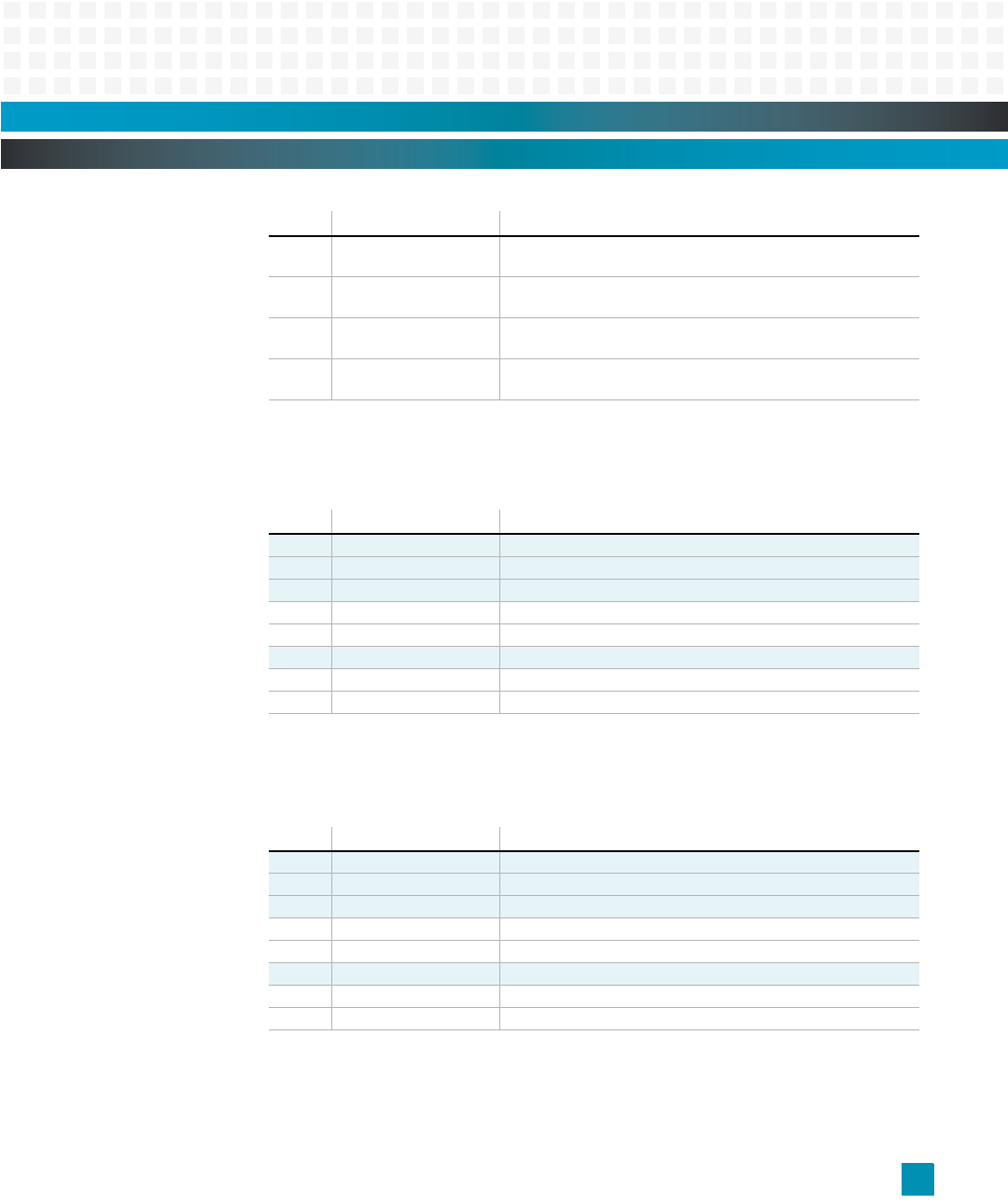

Cavium GPIO Data Out

This register is the data that will be driven on the GPIO line when the Output enable is set.

Register 5-25: Cavium GPIO Data Out (0x84)

Cavium GPIO Data In

This register reads the value on the GPIO lines connected to each Cavium.

Register 5-26: Cavium GPIO Data In (0x88)

3 P2GPIO3OE Processor 2 GPIO3 Output Enable

This is an input from the Cavium to reset the MIP3

2 P1GPIO5OE Processor 1 GPIO5 Output Enable (enabled is the default)

Output enable is set for the TIC timer output to the Cavium

1 P1GPIO4OE Processor 1 GPIO4 Output Enable

This is an input from the Cavium to reset the MIP2

0 P1GPIO3OE Processor 1 GPIO3 Output Enable

This is an input from the Cavium to reset the MIP1

Bits: Function: Description:

7 reserved

6 reserved

5 reserved

4 P2GPIO4 Set the value of the Cavium 2 GPIO bit 4

3 P2GPIO3 Set the value of the Cavium 2 GPIO bit 3

2 reserved

1 P1GPIO4 Set the value of the Cavium 1 GPIO bit 4

0 P1GPIO3 Set the value of the Cavium 1 GPIO bit 3

Bits: Function: Description:

7 reserved

6 reserved

5 reserved

4 P2GPIO4 Read the value of the Cavium 2 GPIO bit 4

3 P2GPIO3 Read the value of the Cavium 2 GPIO bit 3

2 reserved

1 P1GPIO4 Read the value of the Cavium 1 GPIO bit 4

0 P1GPIO3 Read the value of the Cavium 1 GPIO bit 3

Bits: Function: Description: (continued)