Management Complex: Management Processor Header and Serial

ATCA-9305 User’s Manual 10009109-01

4-10

Serial Debug Port

The console port for the management processor is accessible via the front panel mini-B USB

connector P7. The supported baud rates for these ports operate at 9600, 14400, 19200,

38400, 57600, and 115200 bps.

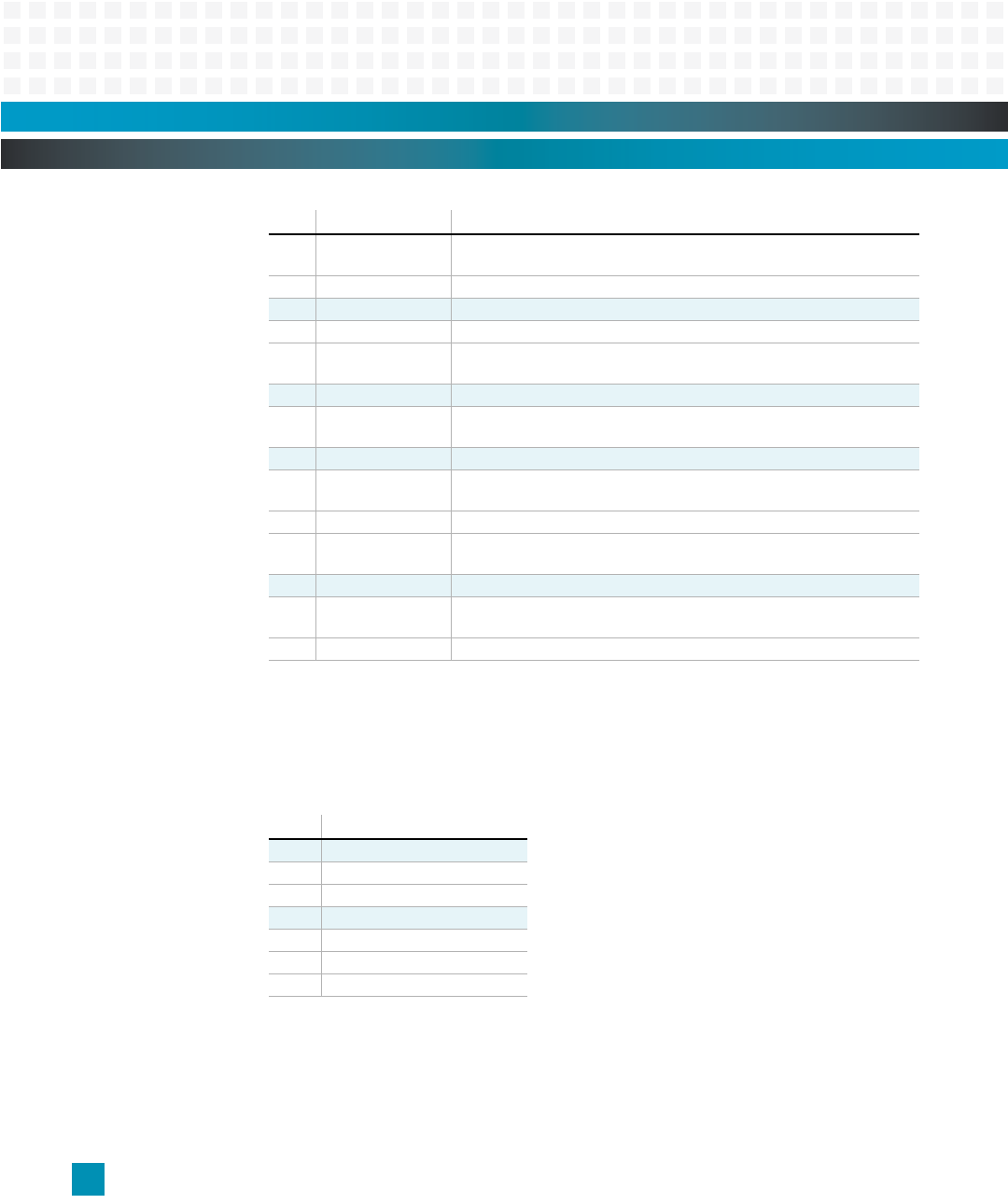

Table 4-8: Serial Debug Connector, P7

3 PQ_TDI Test Data Input is the serial input pin for instructions as well as test and

programming data.

4 DEBUG_TRST* Test Reset input signal resets the test access port.

5 no connect —

6 PQ_JTAG_PWR 3.3 volt power

7 PQ_TCK_R Test Clock Input is the clock input to the boundary scan test (BST)

circuitry.

8 no connect —

9 PQ_TMS Test Mode Select input pin provides the control signal to determine

the transitions of the TAP controller state machine.

10 no connect —

11 DEBUG_SRESET* Soft Reset input signal indicates that the MPC8548 must initiate a

System Reset interrupt.

12 ground —

13 DEBUG_HRESET* Hard Reset input signal indicates that a complete Power-on Reset must

be initiated by the MPC8548.

14 no connect —

15 PQ_CKSTP_OUT* Checkstop Out indicates the MPC8548 has detected a checkstop

condition and has ceased operation.

16 ground —

Pin: Signal:

1 no connect

2 PQ_CONSOLE_RX_C

3 PQ_CONSOLE_TX_C

4 no connect

5 signal ground

6 chassis ground

7 chassis ground

Pin: Signal: Description: (continued)