Register Description

D15343-003 103

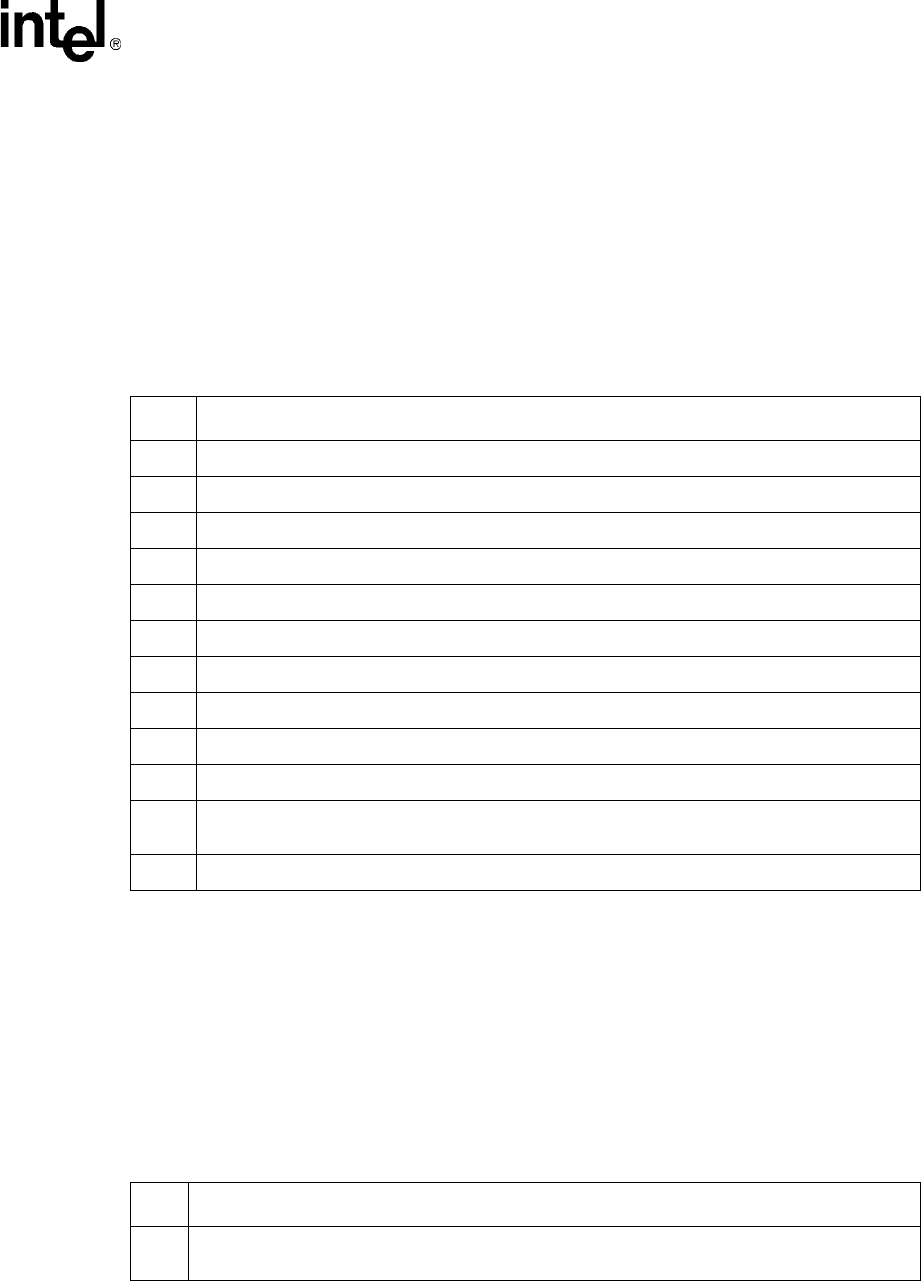

4.11.4 PCISTS – PCI Status Register (Device #2)

PCISTS is a 16-bit status register that reports the occurrence of a PCI compliant master abort and

PCI compliant target abort. PCISTS also indicates the DEVSEL# timing that has been set by the

IGD.

4.11.5 RID – Revision Identification Register (Device #2)

This register contains the revision number of the IGD. These bits are Read Only and Writes to this

register have no effect.

Address Offset:

Default Value:

Access:

Size:

06-07h

0090h

Read Only

16 bits

Bit Description

15 Detected Parity Error (DPE): Since the IGD does not detect parity, this bit is always set to 0.

14 Signaled System Error (SSE) – RO

13 Received Master Abort Status (RMAS) – RO

12 Received Target Abort Status (RTAS) – RO

11 Signaled Target Abort Status (STAS) – RO

10:9 DEVSEL# Timing (DEVT) – RO

8 Data Parity Detected (DPD) – RO

7 Fast Back-to-Back (FB2B) – RO

6 User Defined Format (UDF) – RO

5 66-MHz PCI Capable (66C) – RO

4 CAP LIST: This bit is set to 1 to indicate that the register at 34h provides an offset into the

Function’s PCI Configuration Space containing a pointer to the location of the first item in the list.

3:0 Reserved

Address Offset:

Default Value:

Access:

Size:

08h

02h

Read Only

8 bits

Bit Description

7:0 Revision Identification Number: This is an 8-bit value that indicates the revision identification

number for the GMCH.