Intel

®

82854 Graphics Memory Controller Hub (GMCH)

22 D15343-003

2.2 Processor Host Interface

The Intel

®

82854 GMCH supports the Intel Celeron M Processor, and Genuine Intel Processor.

Key features of the front side bus (FSB) are:

• Support for a 400-MHz system bus frequency.

• Source synchronous double pumped address (2X)

• Source synchronous quad pumped data (4X)

• Front side bus interrupt delivery

• Low voltage swing Vtt (1.05 ~ 1.55V)

• Dynamic Power Down (DPWR#) support

• Integrates AGTL+ termination resistors on all of the AGTL+ signals

• Supports 32-bit host bus addressing allowing the CPU to access the entire 4 GB of the GMCH

memory address space.

• An 8-deep, In-Order queue

• Support DPWR# signal

• Supports one outstanding defer cycle at a time to any particular I/O interface

2.3 GMCH System Memory Interface

The GMCH system memory controller directly supports the following:

• One channel of PC2100/2700 DIMM DDR SDRAM memory

• DDR SDRAM devices with densities of 128-Mb, 256-Mb, and 512-Mb technology

• Up to 1 GB (512-Mb technology) with two DDR DIMMs

• Up to 2 GB (512-Mb technology) using high density devices with two DDR DIMMs

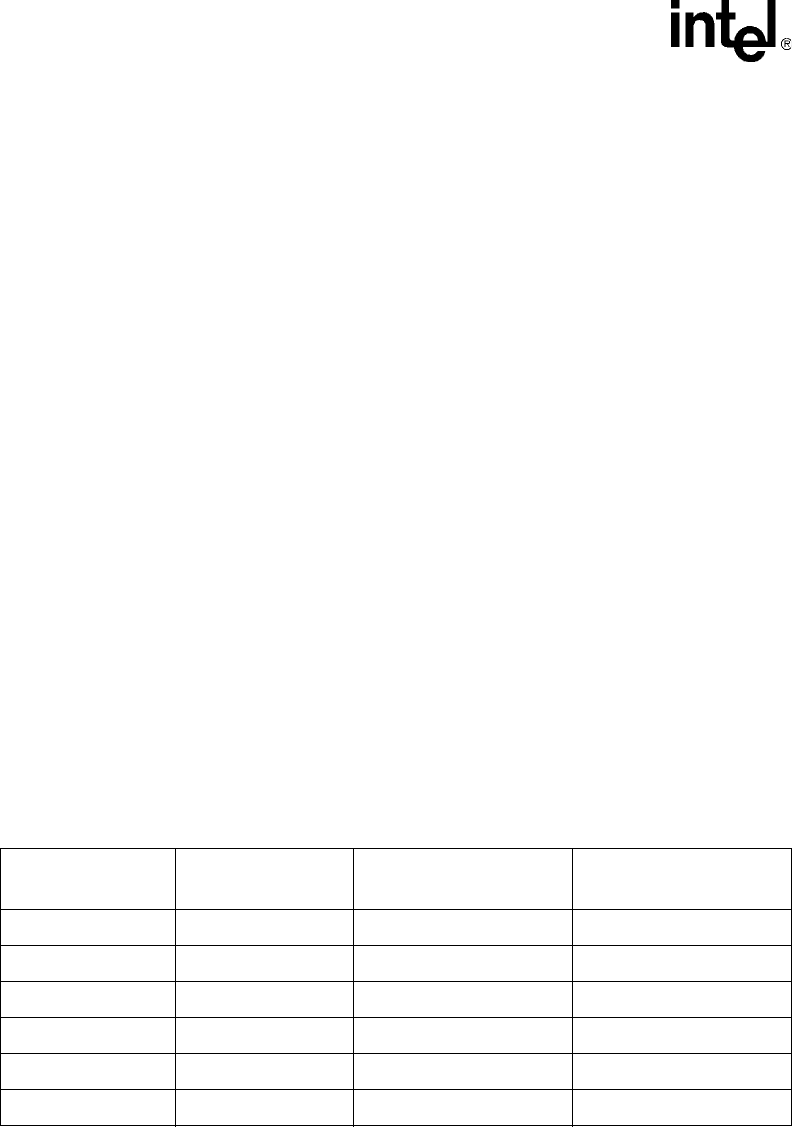

Table 3. DDR SDRAM Memory Capacity

The GMCH system memory interface supports a thermal throttling scheme to selectively throttle

reads and/or writes. Throttling can be triggered either by the on-die thermal sensor, or by preset

write bandwidth limits. Read throttle can also be triggered by an external input pin. The memory

controller logic supports aggressive Dynamic Row Power Down features to help reduce power and

supports Address and Control line tri-stating when DDR SDRAM is in an active power down or in

self refresh state.

Technology Width System Memory Capacity

System Memory Capacity

with Stacked Memory

128 Mb 16 256 MB -

256 Mb 16 512 MB -

512 Mb 16 1 GB -

128 Mb 8 256 MB 512 MB

256 Mb 8 512 MB 1 GB

512 Mb 8 1 GB 2 GB