Introduction

D15343-003 17

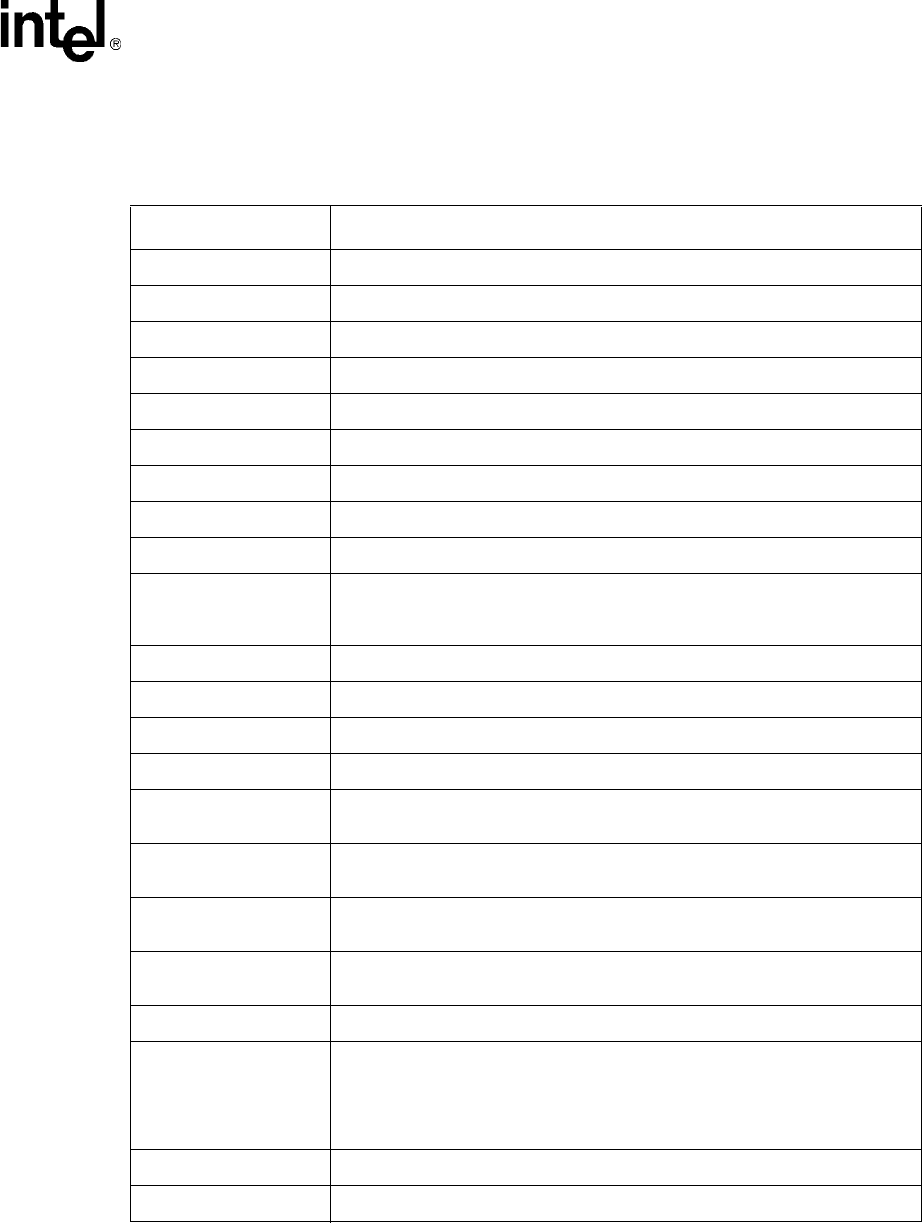

1.2 Terminology

Table 1. Terms and Descriptions

Term Description

AGTL+ Advanced Gunning Transceiver Logic + (AGTL+) bus

BLI Backlight Inverter

Core The internal base logic in the Intel

®

82854 GMCH

CPU Central Processing Unit

CRT Cathode Ray Tube

DBI Dynamic Bus inversion

DBL Display Brightness Link

DDC Display Data Channel (standard created by VESA)

DPMS Display Power Management Signaling (standard created by VESA)

DVI* Digital Visual Interface is the interface specified by the DDWG (Digital Display

Working Group) DVI Spec. Rev. 1.0 utilizing only the Silicon Image developed

TMDS protocol

DVMT Dynamic Video Memory Technology

DVO Digital Video Out

EDID Extended Display Identification Data

EIST Enhanced Intel

®

SpeedStep

®

Technology

FSB Front side bus. Connection between Intel

®

82854 GMCH and the CPU. Also

known as the Host interface

Full Reset A full Intel

®

82854 GMCH Reset is defined in this document when RSTIN# is

asserted

GMCH Refers to the GMCH component. Throughout this datasheet, the Intel

®

82854

Graphics Memory Controller Hub (GMCH) will be referred to as the GMCH.

HD High definition, typically MP@HL for MPEG2; Resolution supported are 720p,

1080i and 1080p

Host This term is used synonymously with processor

Hub Interface (HI) The proprietary interconnect between the Intel

®

82854 GMCH and the ICH4-M

component. In this document, the Hub interface cycles originating from or

destined for the ICH4-M are generally referred to as “Hub interface cycles.” Hub

cycles originating from or destined for the primary PCI interface on are

sometimes referred to as “Hub interface/PCI cycles”

I

2

C Inter-IC (a two wire serial bus created by Philips)

IGD Integrated Graphics Device