Functional Description

D15343-003 123

6.0 Functional Description

6.1 Host Interface Overview

The GMCH front side bus uses source synchronous transfer for the address and data signals. The

address signals are double pumped and two addresses can be generated every bus clock. At

100-MHz bus frequency, the two address signals run at 200 MHz for a maximum address queue

rate of 50-M addresses/sec. The data is quad pumped and an entire 64-B cache line can be

transferred in two bus clocks. At 100-MHz/133MHz bus frequency, the data signals run at

400 MHz for a maximum bandwidth of 3.2/4.3GB/s. The GMCH supports a 8-deep IOQ (In-

Order-Queue) using the Intel Celeron M processor, or Genuine Intel® Processor.

6.2 Dynamic Bus Inversion

The GMCH supports dynamic bus inversion (DBI) when driving and receiving data from the Host

Bus. DBI limits the number of data signals that are driven to a low voltage on each quad pumped

data phase. This decreases the power consumption of the GMCH. DINV[3:0]# indicates if the

corresponding 16 bits of data are inverted on the bus for each quad pumped data phase:

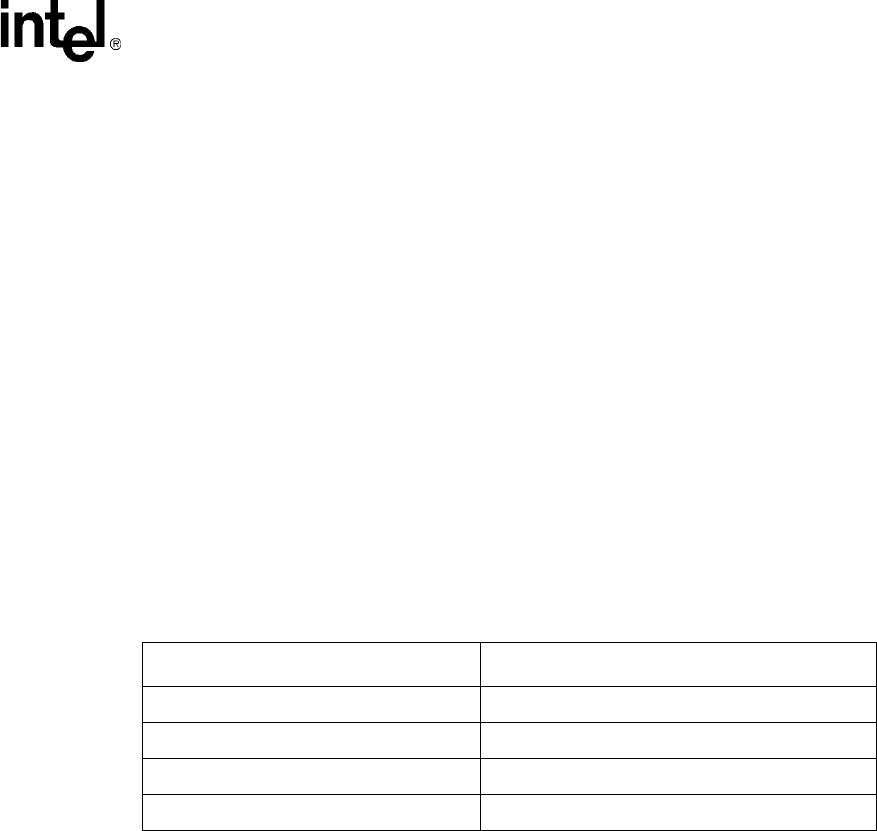

Table 29. Relation of DBI Bits to Data Bits

Whenever the CPU or the GMCH drives data, each 16-bit segment is analyzed. If more than eight

of the 16 signals would normally be driven low on the bus the corresponding DINV# signal will be

asserted and the data will be inverted prior to being driven on the bus. Whenever the CPU or the

GMCH receives data it monitors DINV[3:0]# to determine if the corresponding data segment

should be inverted.

6.2.1 System Bus Interrupt Delivery

The Intel Celeron M processor support system bus interrupt delivery. It does not support the APIC

serial bus interrupt delivery mechanism. Interrupt related messages are encoded on the system bus

as Interrupt Message transactions. System bus interrupts may originate from the processor on the

system bus, or from a downstream device on the Hub interface.

In a GMCH platform, the ICH4-M contains IOxAPICs and its interrupts are generated as upstream

Hub interface Memory Writes. Furthermore, PCI 2.2 defines MSI's (Message Signaled Interrupts)

that are also in the form of Memory Writes. A PCI 2.2 device may generate an interrupt as an MSI

cycle on its PCI bus instead of asserting a hardware signal to the IOxAPIC. The MSI may be

directed to the IOxAPIC, which in turn generates an interrupt as an upstream Hub interface

memory write. Alternatively the MSI may be directed directly to the system bus. The target of an

DINV[3:0] Data Bits

DINV[0]# HD[15:0]#

DINV[1]# HD[31:16]#

DINV[2]# HD[47:32]#

DINV[3]# HD[63:48]#