Intel

®

82854 Graphics Memory Controller Hub (GMCH)

58 D15343-003

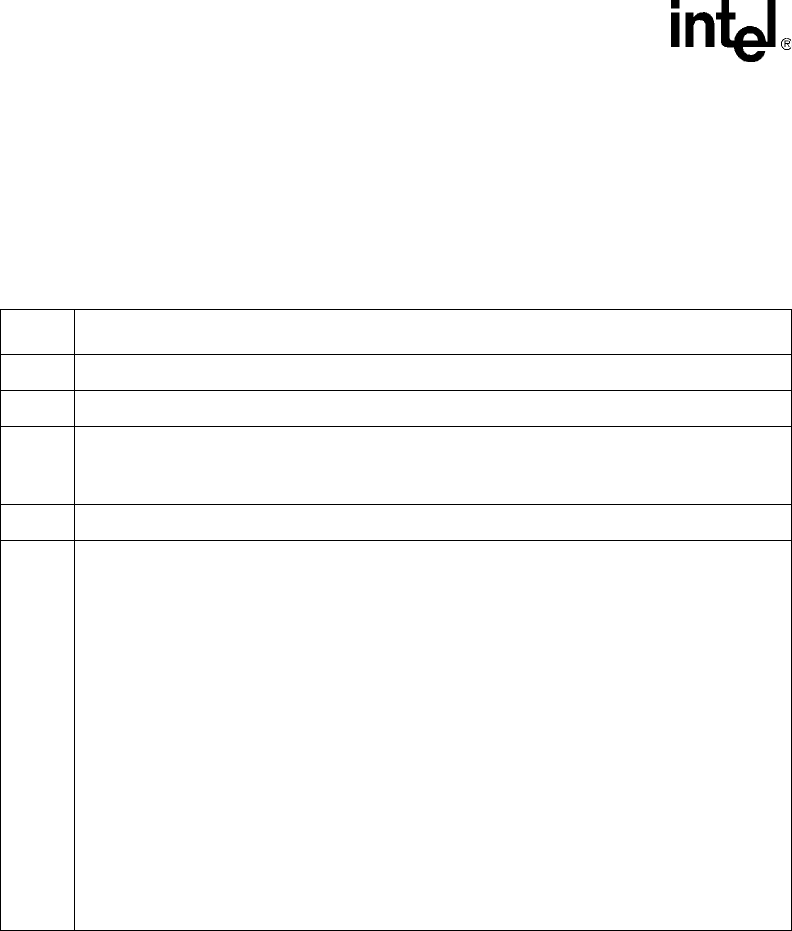

4.8.13 GMC – GMCH Miscellaneous Control Register (Device #0)

Address Offset:

Default Value:

Access:

Size:

50-51h

0000h

Read/Write

16 bits

Bit Descriptions

15:10 Reserved

9 Reserved

8 RRBAR Access Enable—R/W:

1: Enables the RRBAR space.

0: Disable

7:1 Reserved

0 MDA Present (MDAP)—R/W:

This bit should not be set when the VGA Enable bit is not set. If the VGA enable bit is set, then

accesses to IO address range x3BCh–x3BFh are forwarded to Hub interface. If the VGA enable bit

is not set then accesses to IO address range x3BCh–x3BFh are treated just like any other IO

accesses. MDA resources are defined as the following:

Memory: 0B0000h – 0B7FFFh

I/O: 3B4h, 3B5h, 3B8h, 3B9h, 3BAh, 3BFh,

(including ISA address aliases, A[15:10] are not used in decode)

Any I/O reference that includes the I/O locations listed above, or their aliases, will be forwarded to

Hub interface even if the reference includes I/O locations not listed above.

The following table shows the behavior for all combinations of MDA and VGA:

VGA MDA Behavior

0 0 All References to MDA and VGA go to Hub interface (Default)

0 1 Reserved

1 0 All References to VGA go to PCI.

MDA-only references (I/O address 3BF and aliases will go to Hub interface.

1 1 VGA References go to PCI; MDA References go to Hub interface