Intel

®

82854 Graphics Memory Controller Hub (GMCH)

94 D15343-003

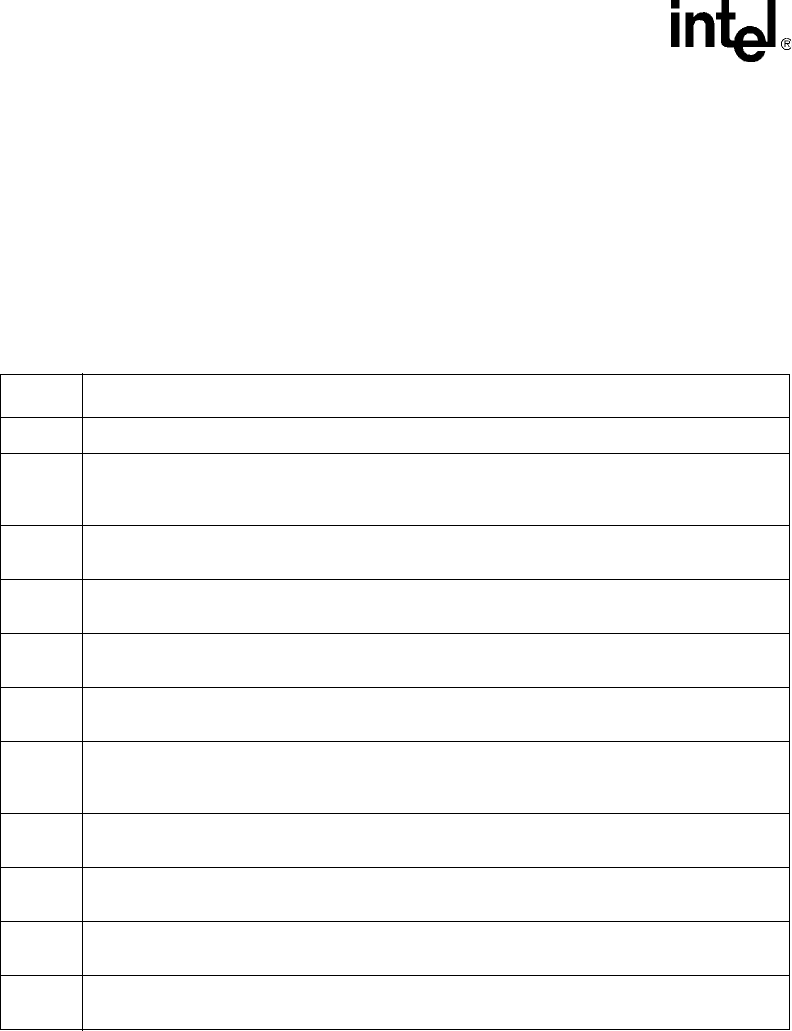

4.10.3 PCICMD – PCI Command Register

Since the Intel

®

82854 GMCH Device #0 does not physically reside on PCI_A many of the bits are

not implemented.

Address Offset:

Default Value:

Access:

Size:

04-05h

0006h

Read Only, Read/Write

16 bits

Bit Descriptions

15:10 Reserved

9 Fast Back-to-Back Enable (FB2B): This bit controls whether or not the master can do fast back-

to-back Write. Since Device #0 is strictly a target, this bit is not implemented and is hardwired to

0. Writes to this bit position have no effect.

8 SERR Enable (SERRE): SERR# is not implemented by Function #1 of Device #0 of the GMCH

and this bit is hardwired to 0. Writes to this bit position have no effect.

7 Address/Data Stepping Enable (ADSTEP): Address/data stepping is not implemented in the

GMCH, and this bit is hardwired to 0. Writes to this bit position have no effect.

6 Parity Error Enable (PERRE): PERR# is not implemented by GMCH and this bit is hardwired to

0. Writes to this bit position have no effect.

5 VGA Palette Snoop Enable (VGASNOOP): The GMCH does not implement this bit and it is

hardwired to a 0. Writes to this bit position have no effect.

4 Memory Write and Invalidate Enable (MWIE): The GMCH will never issue Memory Write and

Invalidate commands. This bit is therefore hardwired to 0. Writes to this bit position will have no

effect.

3 Special Cycle Enable (SCE): The GMCH does not implement this bit and it is hardwired to a 0.

Writes to this bit position have no effect.

2 Bus Master Enable (BME): The GMCH is always enabled as a master on HI. This bit is

hardwired to a 1. Writes to this bit position have no effect.

1 Memory Access Enable (MAE): The GMCH always allows access to Main Memory. This bit is

not implemented and is hardwired to 1. Writes to this bit position have no effect.

0 I/O Access Enable (IOAE): This bit is not implemented in the GMCH and is hardwired to a 0.

Writes to this bit position have no effect.