Intel

®

82854 GMCH System Address Map

D15343-003 119

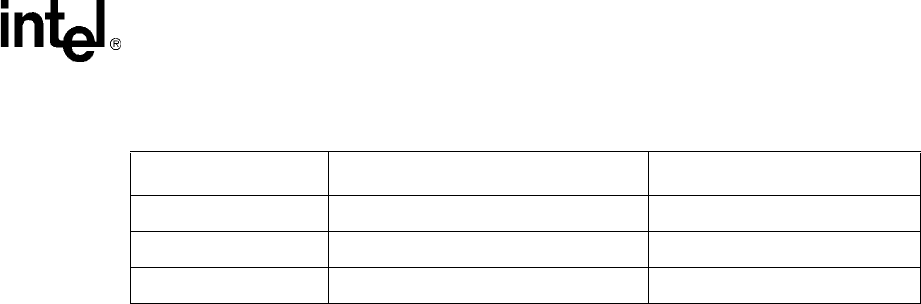

Table 28. SMM Space Transaction Handling

5.4.4 System Memory Shadowing

Any block of system memory that can be designated as Read-Only or Write-Only can be

"shadowed" into GMCH DDR SDRAM. Typically this is done to allow ROM code to execute

more rapidly out of main DDR SDRAM. ROM is used as a Read-Only during the copy process

while DDR SDRAM at the same time is designated Write-Only. After copying, the DDR SDRAM

is designated Read-Only so that ROM is shadowed. CPU bus transactions are routed accordingly.

5.4.5 I/O Address Space

The GMCH does not support the existence of any other I/O devices beside itself on the CPU bus.

The GMCH generates Hub interface or PCI bus cycles for all CPU I/O accesses that it does not

claim. Within the Host bridge the GMCH contains two internal registers in the CPU I/O space,

Configuration Address register (CONFIG_ADDRESS) and the Configuration Data register

(CONFIG_DATA). These locations are used to implement Configuration Space Access

Mechanism and as described in the Configuration register section.

The CPU allows 64 kB +3 B to be addressed within the I/O space. The GMCH propagates the CPU

I/O address without any translation on to the destination bus and therefore provides addressability

for 64 k+3 B locations. Note that the upper three locations can be accessed only during I/O address

wrap-around when CPU bus A16# address signal is asserted. A16# is asserted on the CPU bus

whenever an I/O access is made to 4 bytes from address 0FFFDh, 0FFFEh, or 0FFFFh. A16# is

also asserted when an I/O access is made to 2 bytes from address 0FFFFh.

A set of I/O accesses (other than ones used for configuration space access) is consumed by the

internal graphics device if it is enabled. The mechanisms for internal graphics IO decode and the

associated control is explained later.

The I/O accesses (other than ones used for configuration space access) are forwarded normally to

the Hub interface. The GMCH will not post I/O Write cycles to IDE.

SMM Space Enabled Transaction Address Space (Adr) DRAM Space (DRAM)

Compatible (C) A0000h to BFFFFh A0000h to BFFFFh

High (H) 0FEDA0000h to 0FEDBFFFFh A0000h to BFFFFh

TSEG (T) (TOM-TSEG_SZ) to TOM (TOM-TSEG_SZ) to TOM