Register Description

D15343-003 61

4.8.17 PAM(6:0) – Programmable Attribute Map Register (Device #0)

The GMCH allows programmable DDR SDRAM attributes on 13 Legacy system memory

segments of various sizes in the 640 kB -1 MB address range. Seven Programmable Attribute Map

(PAM) registers are used to support these features. Cacheability of these areas is controlled via the

MTRR registers in the P6 processor. Two bits are used to specify system memory attributes for

each system memory segment. These bits apply to both Host and Hub interface initiator accesses to

the PAM areas. These attributes are:

• RE - Read Enable. When RE = 1, the CPU Read accesses to the corresponding system

memory segment are claimed by the GMCH and directed to main system memory. Conversely,

when RE = 0, the Host Read accesses are directed to PCI0.

• WE - Write Enable. When WE = 1, the Host Write accesses to the corresponding system

memory segment are claimed by the GMCH and directed to main system memory. Conversely,

when WE = 0, the Host Write accesses are directed to PCI0.

The RE and WE attributes permit a system memory segment to be Read Only, Write Only, Read/

Write, or Disabled. For example, if a system memory segment has RE = 1 and WE = 0, the segment

is Read Only.

Each PAM register controls two regions, typically 16 kB in size. Each of these regions has a 4-bit

field. The 4 bits that control each region have the same encoding and are defined in the following

table.

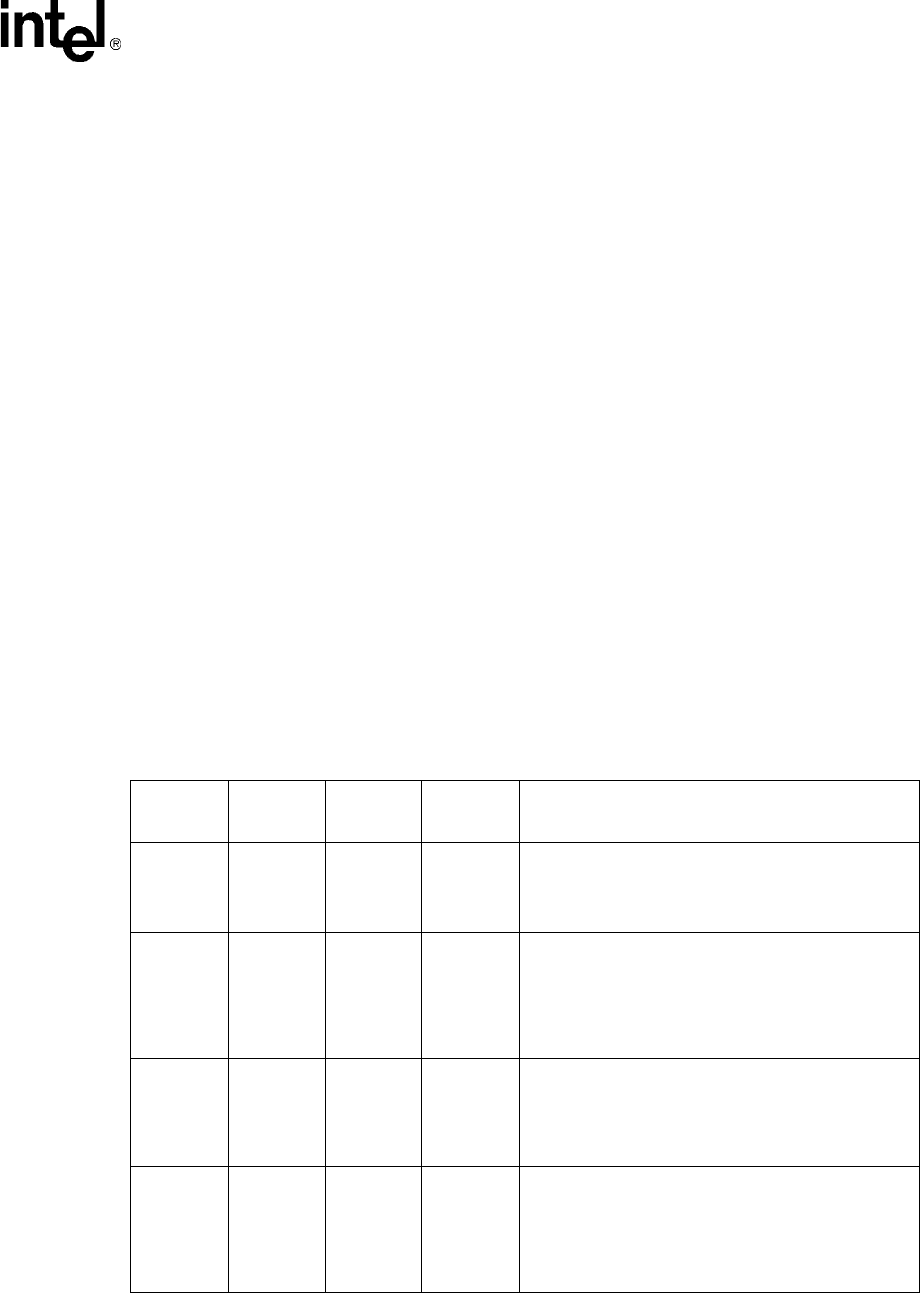

Table 20. Attribute Bit Assignment

Address Offset:

Default Value:

Access:

Size:

59-5Fh

00h Each

Read/Write

4 bits/register, 14 registers

Bits [7, 3]

Reserved

Bits [6, 2]

Reserved

Bits [5, 1]

WE

Bits [4, 0]

RE

Description

XX00Disabled. DDR SDRAM is disabled and all accesses

are directed to Hub interface. The GMCH does not

respond as a Hub interface target for any Read or

Write access to this area.

XX01Read Only. Reads are forwarded to DDR SDRAM

and Writes are forwarded to Hub interface for

termination. This Write protects the corresponding

DDR SDRAM segment. The GMCH will respond as a

Hub interface target for Read accesses but not for

any Write accesses.

XX10Write Only. Writes are forwarded to DDR SDRAM

and Reads are forwarded to the Hub interface for

termination. The GMCH will respond as a Hub

interface target for Write accesses but not for any

Read accesses.

XX11Read/Write. This is the normal operating mode of

main system memory. Both Read and Write cycles

from the host are claimed by the GMCH and

forwarded to DDR SDRAM. The GMCH will respond

as a Hub interface target for both Read and Write

accesses.