Intel

®

854 Graphics Memory Controller Hub (GMCH)

32 D15343-003

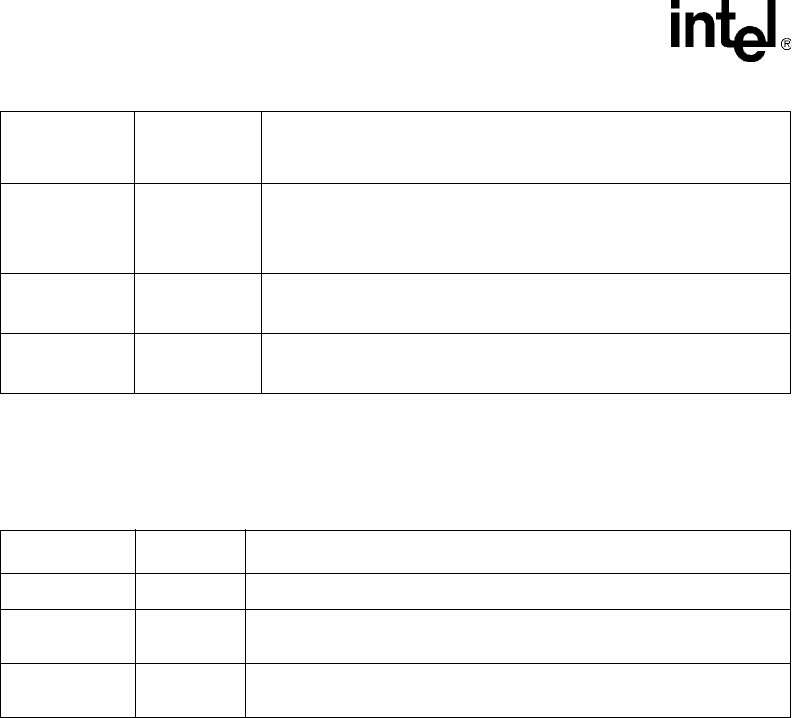

3.3 Hub Interface Signals

Table 7. Hub Interface Signals

SMAB[5,4,2,1] O

SSTL_2

Memory Address Copies: These signals are identical to SMA[5,4,2,1]

and are used to reduce loading for selective CPC(clock-per-command).

These copies are not inverted.

SDM[8:0] O

SSTL_2

Data Mask: When activated during writes, the corresponding data

groups in the DDR SDRAM are masked. There is one SDM for every

eight data lines. SDM can be sampled on both edges of the data

strobes.

RCVENOUT# O

SSTL_2

Clock Output: Reserved, NC.

RCVENIN# O

SSTL_2

Clock Input: Reserved, NC.

Signal Name Type Description

HL[10:0] I/O Hub Packet Data: Data signals used for HI read and write operations.

HLSTB I/O Hub Packet Strobe: One of two differential strobe signals used to transmit or

receive packet data over HI.

HLSTB# I/O Hub Packet Strobe Complement: One of two differential strobe signals used

to transmit or receive packet data over HI.