Intel

®

82854 Graphics Memory Controller Hub (GMCH)

140 D15343-003

6.5.1.3 HSYNC/VSYNC Field Timing

The interlace timing is provided on the timing generator associated with Display Pipe A. When

data is being driven out of the device, HSYNC and VSYNC accompanies or frames the data.

Interlace timing requires that frame data is sent as two fields. Field1 data is scanned out first

followed by Field2. The Pipe A timing produces a field timing signal (Field1) that is used by the

Video Overlay and Display Plane A to produce Field1/Field2 data.

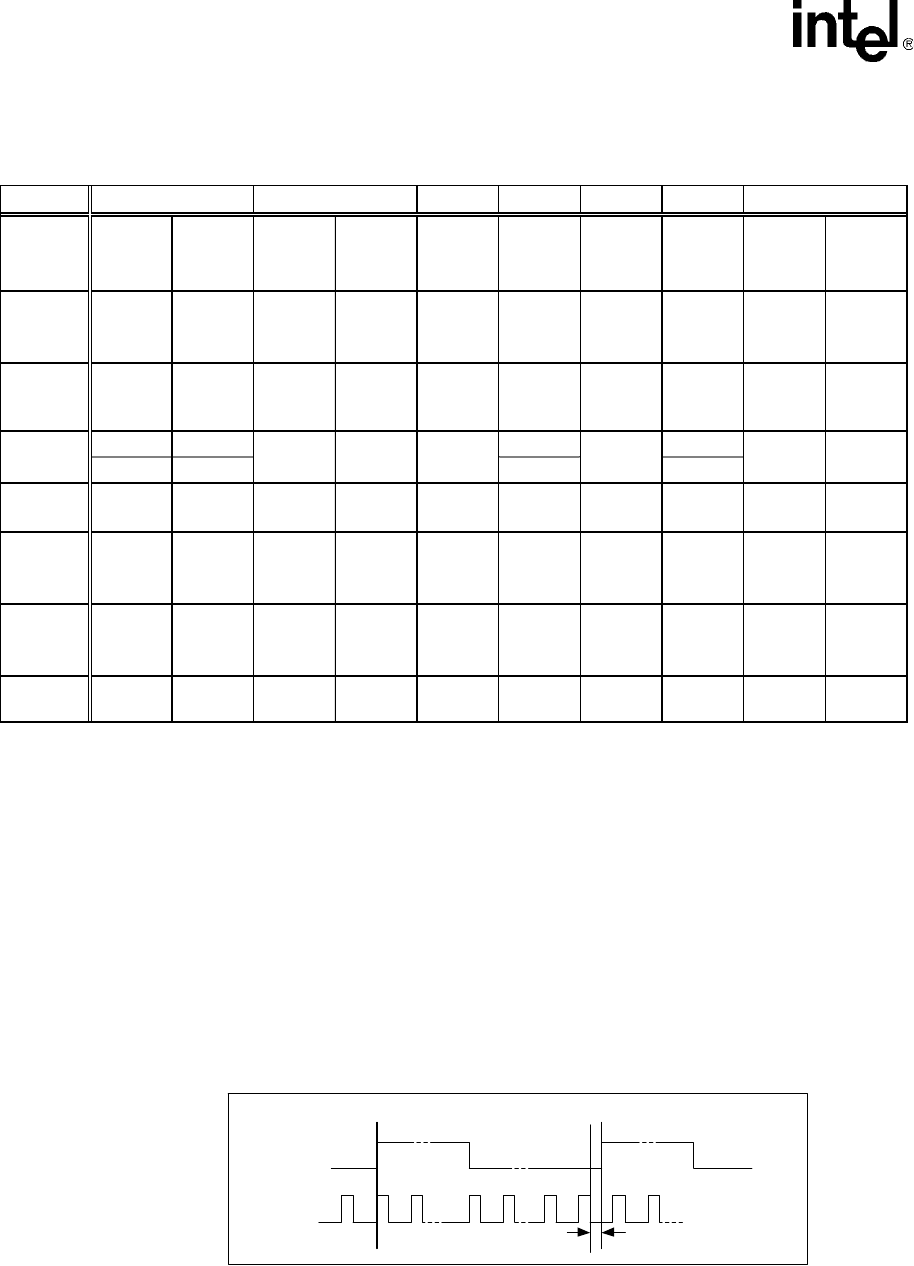

Downstream devices use the relative placement of the VSYNC and HSYNC timing signals to

discern field timing. For Field1 detection, the rising (asserting) edge of VSYNC is coincident with

the rising (asserting) edge of HSYNC. For Field2 detection, VSYNC is asserted after the HSYNC

pulse and occurs after at least 50% of the line is completed (see Figure 10).

Figure 9. H, V Parameters

Parameter

720p 1080i 1080p 576i

Total

Vert ical

Lines 525 525 525 525 750 1125 1125 625 802 805

Act ive

Vert ical

Lines 480 480 480 480 720 1080 1080 576 768 768

Total Blank

Lines45454545304545493437

0-239 0-239 0-539 0-287

263-502 263-502 563-1102 313-600

Total Pixels

per Line 858 858 858 858 1650 2200 2200 864 1688 1656

Active Pixels

per Line 720 640 720 640 1280 1920 1920 720 1280 1366

Blank Pixels

per Line 138 218 138 218 370 280 280 144 408 290

Pixel Clock

[MHz] 13.5 13.5 27 27 74.25 74.25 148.5 13.5 81.23 79.99

480i 480p 768p

Active Line

Number 0-479 0-479 0-719 0-767 0-7670-1079

Figure 10. Interlaced Timing Using HSYNC and VSYNC for Field1/Field2 Downstream

Detection

VSYNC

HSYNC

Field1

Field2

D > 1/2 line