Intel

®

82854 Graphics Memory Controller Hub (GMCH)

64 D15343-003

Extended System BIOS Area (E0000h-EFFFFh)

This 64-kB area is divided into four 16-kB segments that can be assigned with different attributes

via PAM Control register as defined in Figure 4 and Table 21.

System BIOS Area (F0000h-FFFFFh)

This area is a single 64-kB segment that can be assigned with different attributes via PAM Control

register as defined in Figure 4 and Table 21.

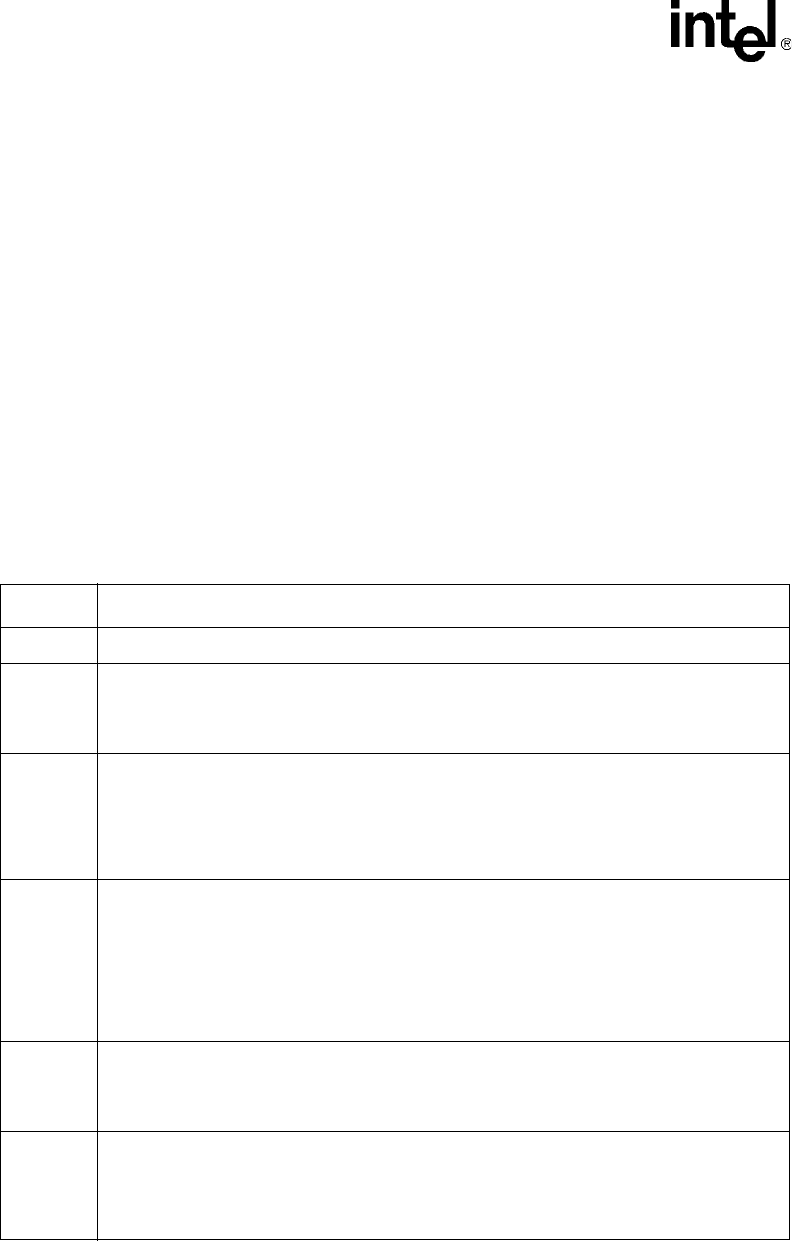

4.8.18 SMRAM – System Management RAM Control Register (Device #0)

The SMRAM register controls how accesses to Compatible and Extended SMRAM spaces are

treated. The Open, Close, and Lock Bits function only when G_SMRAME Bit is set to a 1. Also,

the Open Bit must be Reset before the LOCK Bit is set.

Address Offset:

Default Value:

Access:

Size:

60h

02h

Read/Write/Lock, Read Only

8 bits

Bit Description

7 Reserved

6 SMM Space Open (D_OPEN): When D_OPEN=1 and D_LCK=0, the SMM space DDR

SDRAM is made visible even when SMM decode is not active. This is intended to help BIOS

initialize SMM space. Software should ensure that D_OPEN=1 and D_CLS=1 are not set at the

same time. When D_LCK is set to a 1, D_OPEN is Reset to 0 and becomes Read Only.

5 SMM Space Closed (D_CLS): When D_CLS = 1 SMM Space, DDR SDRAM is not accessible

to data references, even if SMM decode is active. Code references may still access SMM

space DDR SDRAM. This will allow SMM software to reference “through” SMM space to

update the display even when SMM is mapped over the VGA range. Software should ensure

that D_OPEN=1 and D_CLS=1 are not set at the same time. D_CLS applies to all SMM spaces

(Cseg, Hseg, and Tseg).

4 SMM Space Locked (D_LCK): When D_LCK is set to 1, then D_OPEN is Reset to 0 and

D_LCK, D_OPEN, G_SMRAME, C_BASE_SEG, GMS, DRB, DRA, H_SMRAM_EN, TSEG_SZ

and TSEG_EN become Read Only. D_LCK can be set to 1 via a normal Configuration Space

Write but can only be cleared by a Full Reset. The combination of D_LCK and D_OPEN

provide convenience with security. The BIOS can use the D_OPEN function to initialize SMM

space and then use D_LCK to “lock down” SMM space in the future so that no application

software (or BIOS itself) can violate the integrity of SMM space, even if the program has

knowledge of the D_OPEN function.

3 Global SMRAM Enable (G_SMRAME): If set to a 1, then Compatible SMRAM functions is

enabled, providing 128 kB of DDR SDRAM accessible at the A0000h address while in SMM

(ADS# with SMM decode). To enable Extended SMRAM function this bit must be set to 1, refer

to the section on SMM for more details. Once D_LCK is set, this bit becomes Read Only.

2:0 Compatible SMM Space Base Segment (C_BASE_SEG)—RO: This field indicates the

location of SMM space. “SMM DRAM” is not remapped. It is simply “made visible” if the

conditions are right to access SMM space, otherwise the access is forwarded to Hub interface.

C_BASE_SEG is hardwired to 010 to indicate that the GMCH supports the SMM space at

A0000h–BFFFFh.