Functional Description

D15343-003 125

series of I/O cycles to the south bridge. The BIOS needs to determine the size and type of system

memory used for each of the rows of system memory in order to properly configure the GMCH

system memory interface.

For SMBus Configuration and Access of the Serial Presence Detect Ports, refer to the Intel®

82801DBM I/O Controller Hub 4 (ICH4-M) Datasheet (252337) for more detail.

6.3.2.2 System Memory Register Programming

This section provides an overview of how the required information for programming the DDR

SDRAM registers is obtained from the Serial Presence Detect ports on the DDR DIMMs. The

Serial Presence Detect ports are used to determine Refresh Rate, MA and MD Buffer Strength, row

Type (on a row by row basis), DDR SDRAM Timings, row sizes and row page sizes. Table 30 lists

a subset of the data available through the on board Serial Presence Detect ROM on each DDR

DIMM.

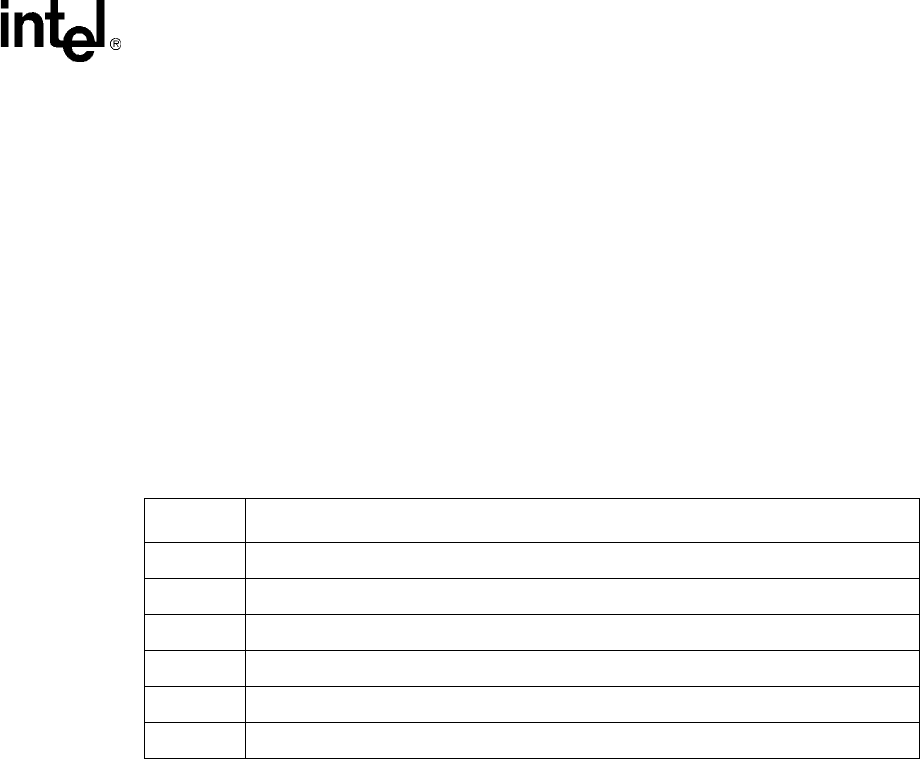

Table 30. Data Bytes on DDR DIMM Used for Programming DRAM Registers

Table 30 is only a subset of the defined SPD bytes on the DDR DIMMs. These bytes collectively

provide enough data for programming the GMCH DDR SDRAM registers.

6.3.3 DDR SDRAM Performance Description

The overall system memory performance is controlled by the DDR SDRAM timing register,

pipelining depth used in GMCH, system memory speed grade and the type of DDR SDRAM used

in the system. Besides this, the exact performance in a system is also dependent on the total system

memory supported, external buffering and system memory array layout. The most important

contribution to overall performance by the system memory controller is to minimize the latency

required to initiate and complete requests to system memory, and to support the highest possible

bandwidth (full streaming, quick turn-arounds). One measure of performance is the total flight

time to complete a cache line request. A true discussion of performance really involves the entire

chipset, not just the system memory controller.

Byte Function

2 System Memory Type (DDR SDRAM)

3 Number of row addresses, not counting Bank Addresses

4 Number of Column Addresses

5 Number of DIMM banks

12 Refresh Rate/Type

17 Number Banks on each Device