2 Troubleshooting Procedures 2.4 System Board Troubleshooting

2-20 PORTEGE A100 Maintenance Manual (960-460)

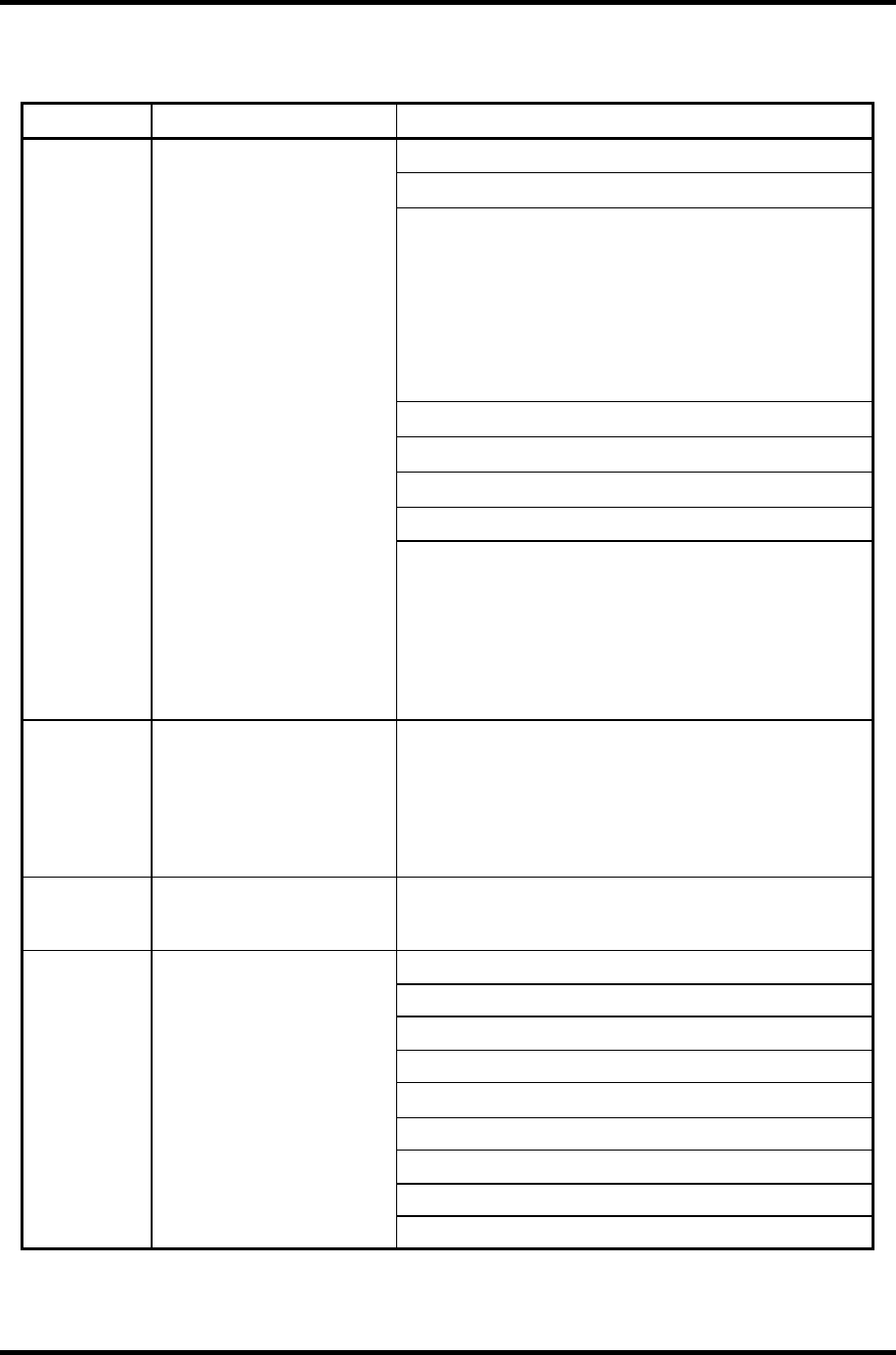

Table 2-3 D port status (1/7)

D port status

Inspection items Details

Clearing a software reset bit

Enabling address line A20

Initializing Ali

Initializing Intel North Bridge

Setting LPC port

Disabling AC’97 Modem/Audio

Corresponding KBC Serial IRQ

Setting of enabling PM timer

Dummy-reading 3

rd

Bus date

Initializing debug port

Initializing the CH0 of a PIT

Initializing flags determining whether BIOS is rewritten

F000h Start

CHECK SUM CHECK

Switching to protected mode

Examining the checksum of BootBlock (skips when S3

returns), HLT at checksum error

Examining the checksum of other data in a flash memory

(skips when S3 returns)

F001h Checking if EC/KBC

firmware is to be rewritten

Checking if EC/KBC firmware is to be rewritten

When is to be rewritten, goes to Rewriting BIOS routine.

When S3 returns, moves the process to the System BIOS

IRT side.

Initializing a KBC

Enabling KB

F002h Checking whether BIOS

rewrite is requested

Checking if BIOS is to be rewritten

When rewriting by checksum error other than of BootBlock

or a user is requested, goes to BIOS rewriting process.

Changing the process to the System BIOS IRT side

Initializing specific for the system

Selecting USB controller clock

Initializing HW specific for model

Initializing PIT channel 1 ( Refresh interval→30µs)

Initializing PIT, DMAC, PIC

Enabling L1 Cache

Clearing memory

F003h

Moving to real mode and copying BIOS to RAM