CHAPTER 8: DEBUGGER

152 EPSON S5U1C63000A MANUAL

(S1C63 FAMILY ASSEMBLER PACKAGE)

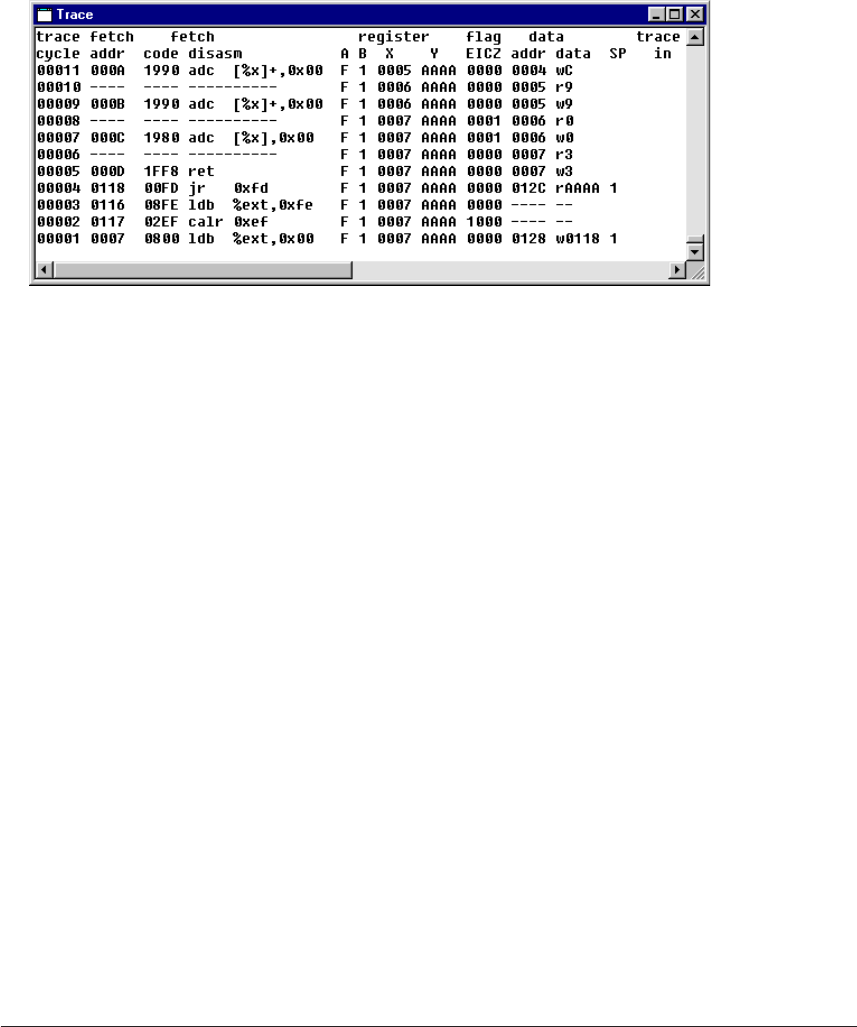

8.8.6 Trace Functions

The debugger has a function to trace program execution.

Trace memory and trace information

The ICE contains a trace memory. When the program executes instructions in the trace range

according to the trace mode, the trace information on each cycle is taken into this memory. The trace

memory has the capacity to store information for 8,192 cycles, making it possible to trace up to 4,096

instructions (for two-clock instructions only). When the trace information exceeds this capacity, the

data is overwritten, the oldest data first unless operating in single-delay trigger mode. Consequently,

the trace information stored in the trace memory is always within 8,192 cycles. The trace memory is

cleared when a program is executed, starting to trace the new execution data.

The following lists the trace information that is taken into the trace memory in every cycle. This list is

corresponded to display in the [Trace] window.

trace cycle: Trace cycle (decimal). The last information taken into the trace memory becomes

00001.

fetch addr: Fetch address (hexadecimal).

fetch code disasm:Fetch code (hexadecimal) and disassembled content.

register: Values of A, B, X, and Y registers after cycle execution (hexadecimal).

flag: States of E, I, C, and Z flags after cycle execution (binary).

data: Accessed data memory address (hexadecimal), read/write (denoted by r or w at

the beginning of data), and data (1-digit hexadecimal for 4-bit access; 4-digit

hexadecimal for 16-bit access).

SP: Stack access (1 for SP1 access; 2 for SP2 access).

trace in: Input to TRCIN pin (denoted by L when low-level signal is input).

Notes: The S1C63000 CPU uses two-stage pipelined instruction processing, one for fetch and one for

execution. Therefore, please pay attention to the following:

• The CPU fetches the next instruction in the last execution cycle of an instruction. Because the

instruction is executed beginning from the cycle which is after the fetch, the displayed states of

the registers, etc. are not the execution results of the fetch instruction that is displayed on the

same line.

• For reasons of the ICE operation timing, the trace data at the boundary of operations, such

as in the fetch cycle at which trace starts or the execution cycle at which trace ends, will not

always be stored in memory.