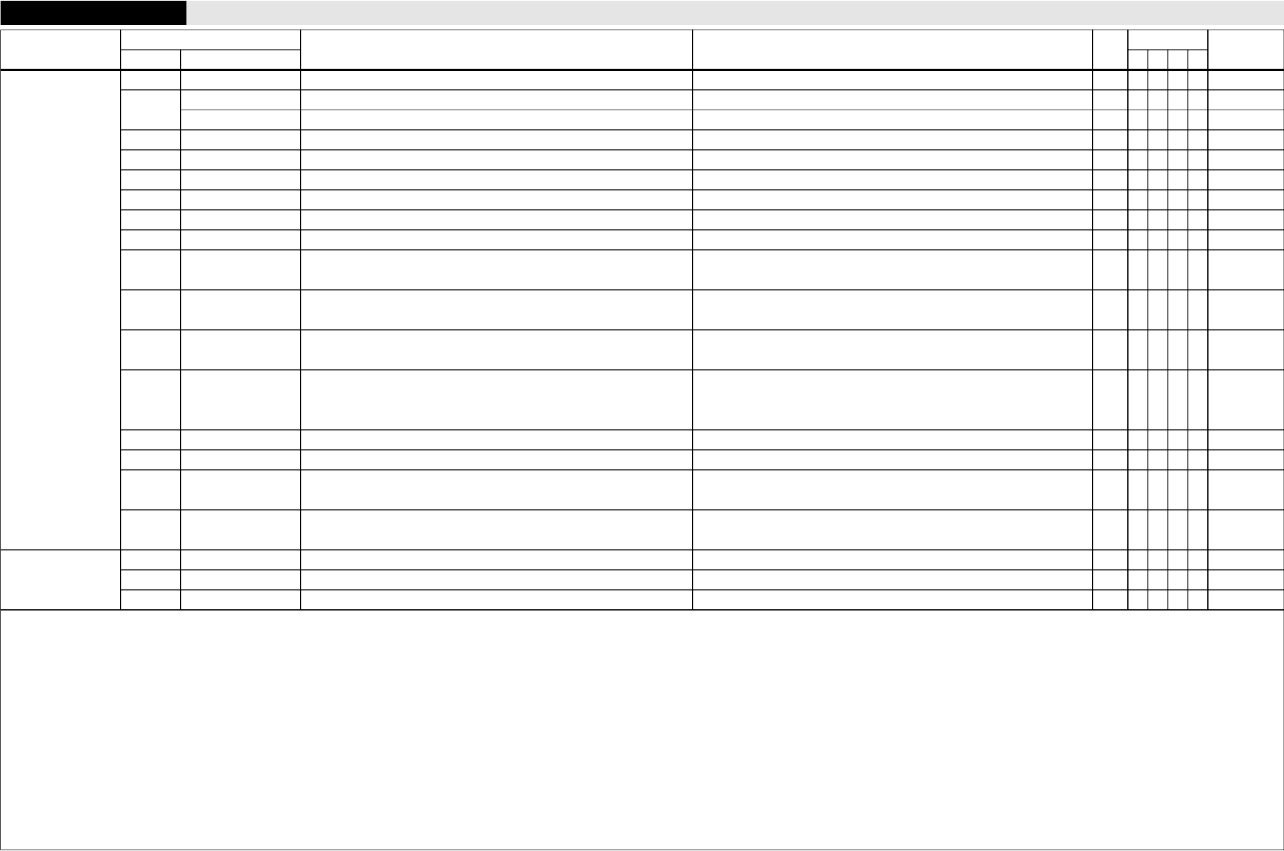

Instruction List (13)

S1C63000 Core CPU

Opcode

JR

JR

JR

JRC

JRNC

JRZ

JRNZ

JP

CALZ

CALR

CALR

INT

RET

RETS

RETD

RETI

HALT

SLP

NOP

Operand

sign8

%A

%BA

[00addr6]

sign8

sign8

sign8

sign8

%Y

imm8

sign8

[00addr6]

imm6

imm8

Basic function

PC ← PC+sign8+1 (sign8=-128~127)

PC ← PC+A+1

PC ← PC+BA+1

PC ← PC+[00addr6]+1

If C=1 then PC

← PC+sign8+1 (sign8=-128~127)

If C=0 then PC

← PC+sign8+1 (sign8=-128~127)

If Z=1 then PC

← PC+sign8+1 (sign8=-128~127)

If Z=0 then PC

← PC+sign8+1 (sign8=-128~127)

PC ← Y

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1, SP1 ← SP1-1,

PC ← imm8

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1, SP1 ← SP1-1,

PC ← PC+sign8+1 (sign8=-128~127)

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1, SP1 ← SP1-1,

PC ← PC+[00addr6]+1

[SP2-1] ← F, SP2 ← SP2-1,

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1, SP1 ← SP1-1,

PC ← imm6 (imm6=0100H~013FH)

PC ← ([SP1∗4+3]~[SP1∗4]), SP1 ← SP1+1

PC ← ([SP1∗4+3]~[SP1∗4]), SP1 ← SP1+1, PC ← PC+1

PC ← ([SP1∗4+3]~[SP1∗4]), SP1 ← SP1+1

[X] ← i3~0, [X+1] ← i7~4, X ← X+2

PC ← ([SP1∗4+3]~[SP1∗4]), SP1 ← SP1+1

F ← [SP2], SP2 ← SP2+1

Halt

Sleep

No operation (PC

← PC+1)

Extended function

(when "LDB %EXT, imm8" is executed)

PC ← PC+sign16+1 (sign16=-32768~32767)

*

1

–

–

–

If C=1 then PC

← PC+sign16+1 (sign16=-32768~32767)

*

1

If C=0 then PC

← PC+sign16+1 (sign16=-32768~32767)

*

1

If Z=1 then PC

← PC+sign16+1 (sign16=-32768~32767)

*

1

If Z=0 then PC

← PC+sign16+1 (sign16=-32768~32767)

*

1

–

–

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1, SP1 ← SP1-1,

PC ← PC+sign16+1 (sign16=-32768~32767)

*

–

–

–

–

–

–

–

–

–

–

–

–

–

–

Symbol

●,@rl

–

–

●

●,@rl

●,@rl

●,@rl

●,@rl

–

●

●,@rl

●

–

–

–

●,@h,@l

–

–

–

–

Clk

1

1

1

2

1

1

1

1

1

1

1

2

3

1

2

3

2

2

2

1

C

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

↔

–

–

–

Z

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

↔

–

–

–

E

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

↔

0

0

0

I

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

↔

–

–

–

Mnemonic

Classification

Branch control

System

control

Flags

Remarks

∗1: sign16(s15–s8) = imm8, sign16(s7–s0) = sign8