R61509V Target Spec

Rev. 0.11 April 25, 2008, page 100 of 181

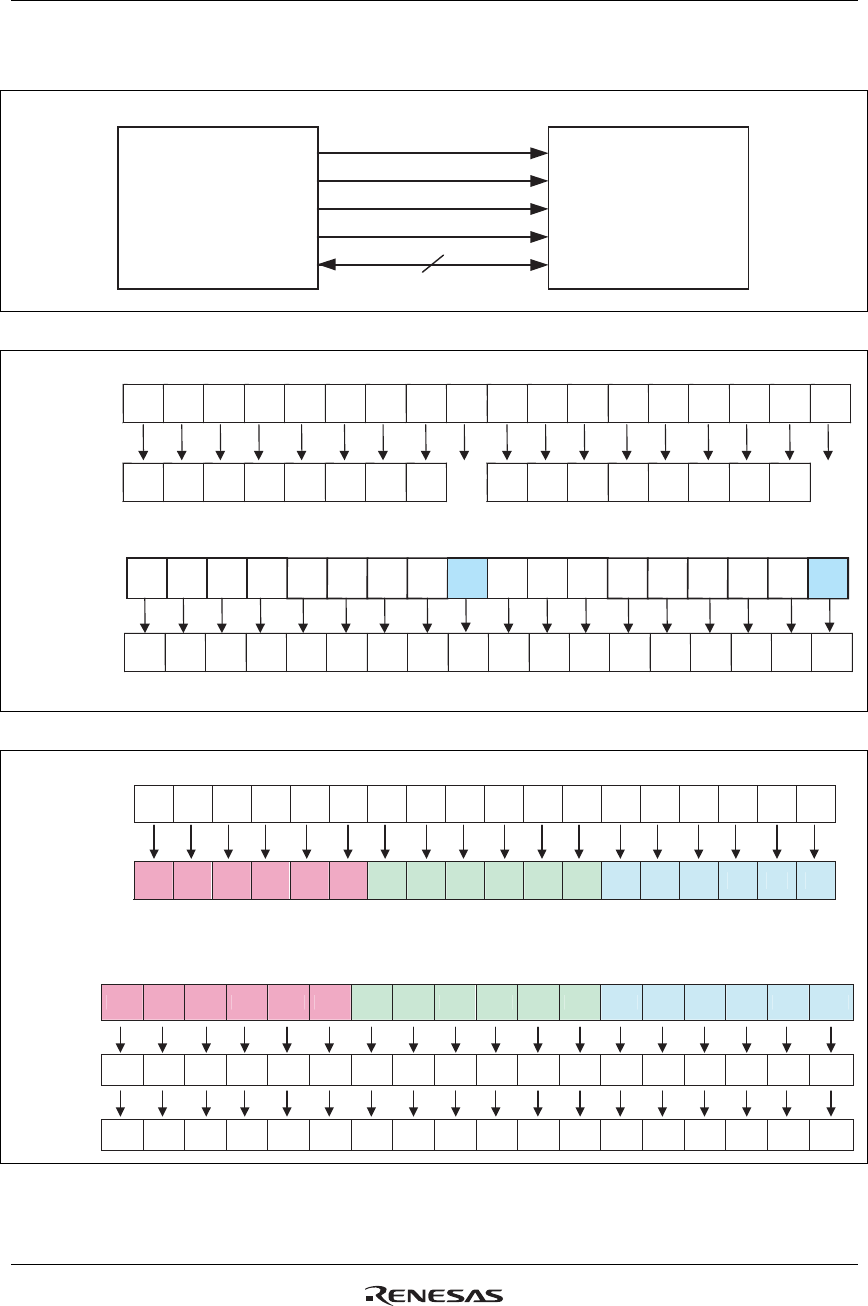

80-System 18-bit Bus Interface

A1

HWR

RS

WRX

18

R61509V

HOST

PROCESSOR

IM[2:0] = 000

CSn

(RDX) (RDX)

D31-0

CSX

DB17-0

Figure 14 18-bit Interface

Instruction write

DB

17

DB

16

DB

15

DB

14

DB

13

DB

12

DB

11

DB

10

DB

9

DB

8

DB

7

DB

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

IB

15

IB IB

13

IB

12

IB

11

IB

10

IB

9

IB

8

IB

7

IB

6

IB

5

IB

4

IB

3

IB

2

IB

1

IB

0

14

6

Device code read / Instruction read

DB

17

DB

16

DB

15

DB

14

DB

13

DB

12

DB

11

DB

10

DB

9

DB

8

DB

7

DB

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

IB

15

IB IB

13

IB

12

IB

11

IB

10

IB

9

IB

8

IB

7

IB

6

IB

5

IB

4

IB

3

IB

2

IB

1

IB

0

14

6

Instruction code

Instruction code

Input

Instruction

Device code

Output

Figure 15 18-bit Interface Data Format (Instruction Write / Device Code Read / Instruction Read)

DB

17

DB DB

DB

14

DB

13

DB

12

DB

11

DB

10

DB

9

DB

8

DB

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

R5 R4 R3 R2 R1 R0 G5 G4 G3 G2 G1 G0 B5 B4 B3 B2 B1 B0

RAM data write

7

16

15

RAM data read

GRAM write

data

Input

R5 R4 R3 R2 R1 R0 G5 G4 G3 G2 G1 G0 B5 B4 B3 B2 B1 B0

RD

[17]

RD

[16]

RD

[15]

RD

[14]

RD

[13]

RD

[12]

RD

[11]

RD

[10]

RD

[9]

RD

[8]

RD

[7]

RD

[6]

RD

[5]

RD

[4]

RD

[3]

RD

[2]

RD

[1]

RD

[0]

DB

17

DB

16

DB

15

DB

14

DB

13

DB

12

DB

11

DB

10

DB

9

DB

8

DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

GRAM data

Read data

Output pins

Note: Normal display in 262,144 colors.

1 pixel

Figure 16 18-bit Interface Data Format (RAM Data Write / RAM Data Read)