R61509V Target Spec

Rev. 0.11 April 25, 2008, page 122 of 181

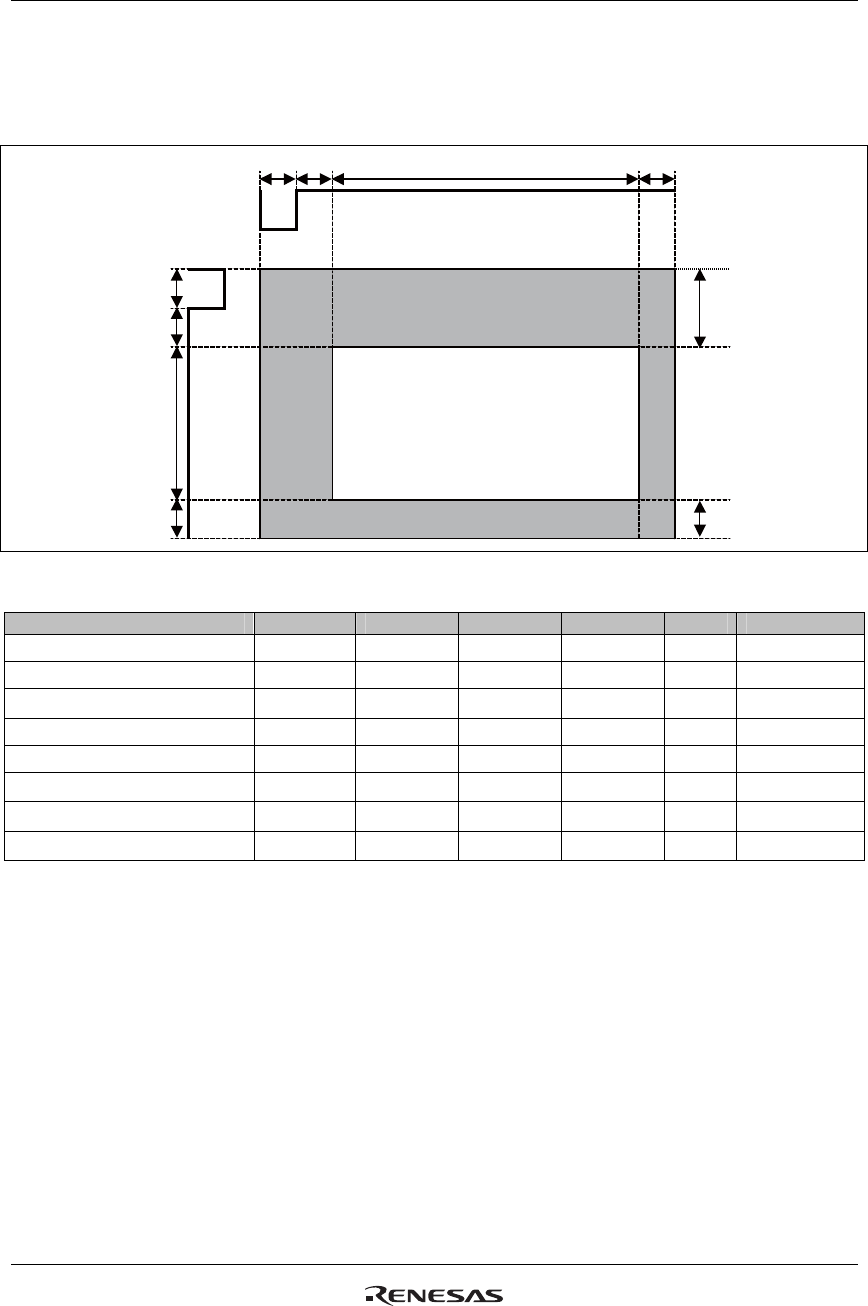

Polarities of VSYNCX, HSYNCX, ENABLE, and DOTCLK Signals

The polarities of VSYNCX, HSYNCX, ENABLE, and DOTCLK signals can be changed by setting the

DPL, EPL, HSPL, and VSPL bits, respectively for convenience of system configuration.

㪧㪝㪟㫉㪻㪘㪟㪧㪙㪟㪺㫅㫐㫊㪟

㪭㫊㫐㫅㪺

㪙㪧

㪭㪙㪧

㪭㪘㪻㫉

㪭㪝㪧 㪝㪧

Valid data period

Figure 43

Table 63

Parameters Symbols Min. Typ. Max. Step Unit

Horizontal Synchronization Hsync 2 10 16 1 DOTCLKCYC

Horizontal Back Porch HBP 2 20 24 1 DOTCLKCYC

Horizontal Address

HAdr - 240 - 1 DOTCLKCYC

Horizontal Front Porch HFP 2 10 16 1 DOTCLKCYC

Vertical Synchronization Vsync 1 2 4 1 Line

Vertical Back Porch

VBP 1 2 - 1 Line

Vertical Address

VAdr - 432 - 1 Line

Vertical Front Porch

VFP 3 4 - 1 Line

Note: The values of typ. are based on the following conditions; the panel resolution is QVGA (240 ×

432), the clock frequency is 7.39MHz, and the frame frequency is about 60Hz.)

Vsync + VBP = BP. VFP = FP. Vadr = NL.

(Number of clocks per 1H) ≥ (Number of RTN clocks) × (1/1 div.) × (PCDIVL + PCDIVH)

The setting example is shown in the following page.