R61509V Target Spec

Rev. 0.11 April 25, 2008, page 97 of 181

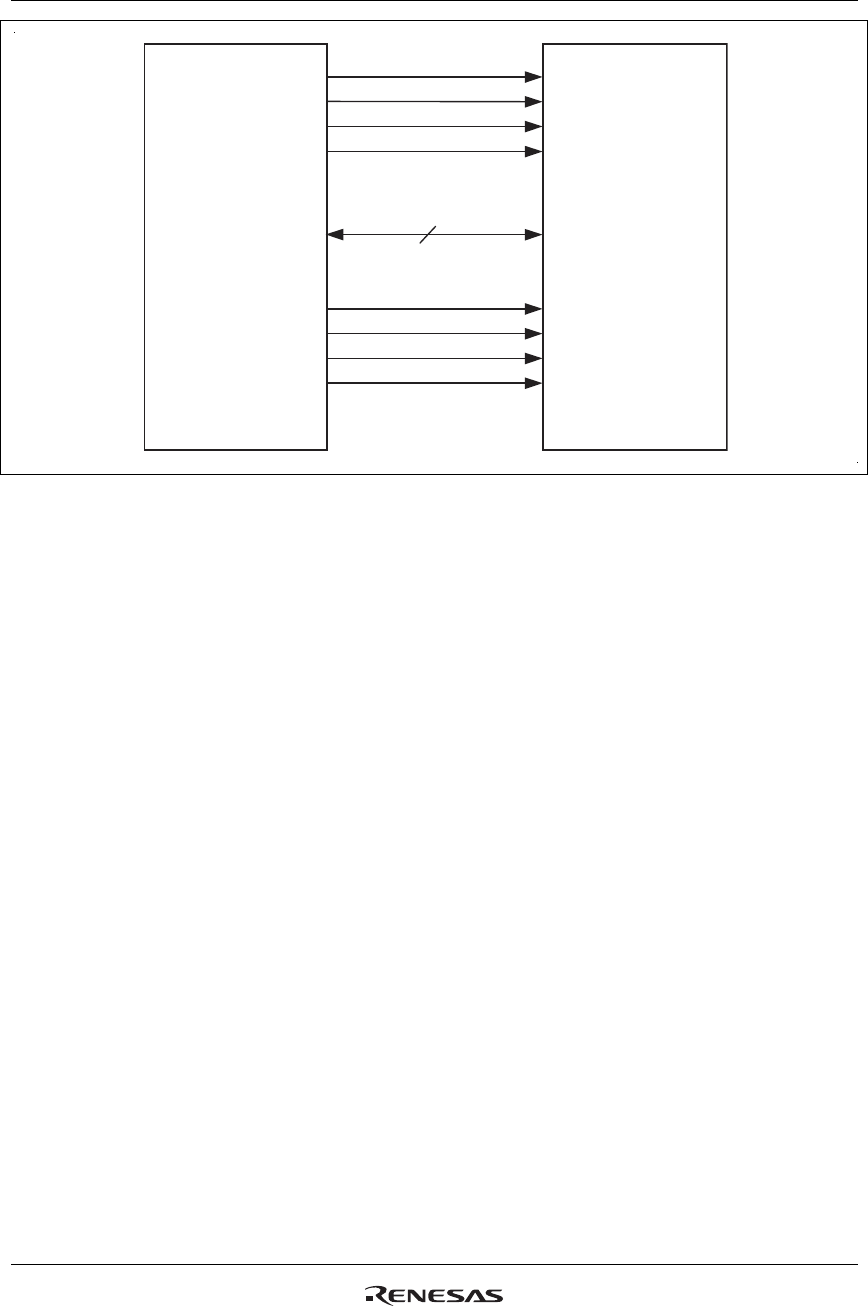

CSX

RS

WRX

R61509V

System interface

18/16/9/8

RGB interface

18/16

DB17-0

(RDX)

ENABLE

VSYNCX

HSYNCX

DOTCLK

System

interface

RGB

interface

System

Figure 13

Internal clock operation

The display operation is synchronized with signals generated from internal oscillator’s clock (OSC) in this

mode. All input via external display interface is disabled in this operation. The internal RAM can be

accessed only via system interface.

RGB interface operation (1)

The display operation is synchronized with frame synchronous signal (VSYNCX), line synchronous signal

(HSYNCX), and dot clock signal (DOTCLK) in RGB interface operation. These signals must be supplied

during the display operation via RGB interface.

The R61509V transfers display data in units of pixels via DB17-0 pins. The display data is stored in the

internal RAM. The combined use of window address function can minimize the total number of data

transfer for moving picture display by transferring only the data to be written in the moving picture RAM

area when it is written and enables the R61509V to display a moving picture and the data in other than the

moving picture RAM area simultaneously.

The front porch (FP), back porch (BP), and the display (NL) periods are automatically calculated inside the

R61509V by counting the number of clocks of line synchronous signal (HSYNCX) from the falling edge of

the frame synchronous signal (VSYNCX). Make sure to transfer pixel data via DB17-0 pins in accordance

with the setting of these periods.