R61509V Target Spec

Rev. 0.11 April 25, 2008, page 177 of 181

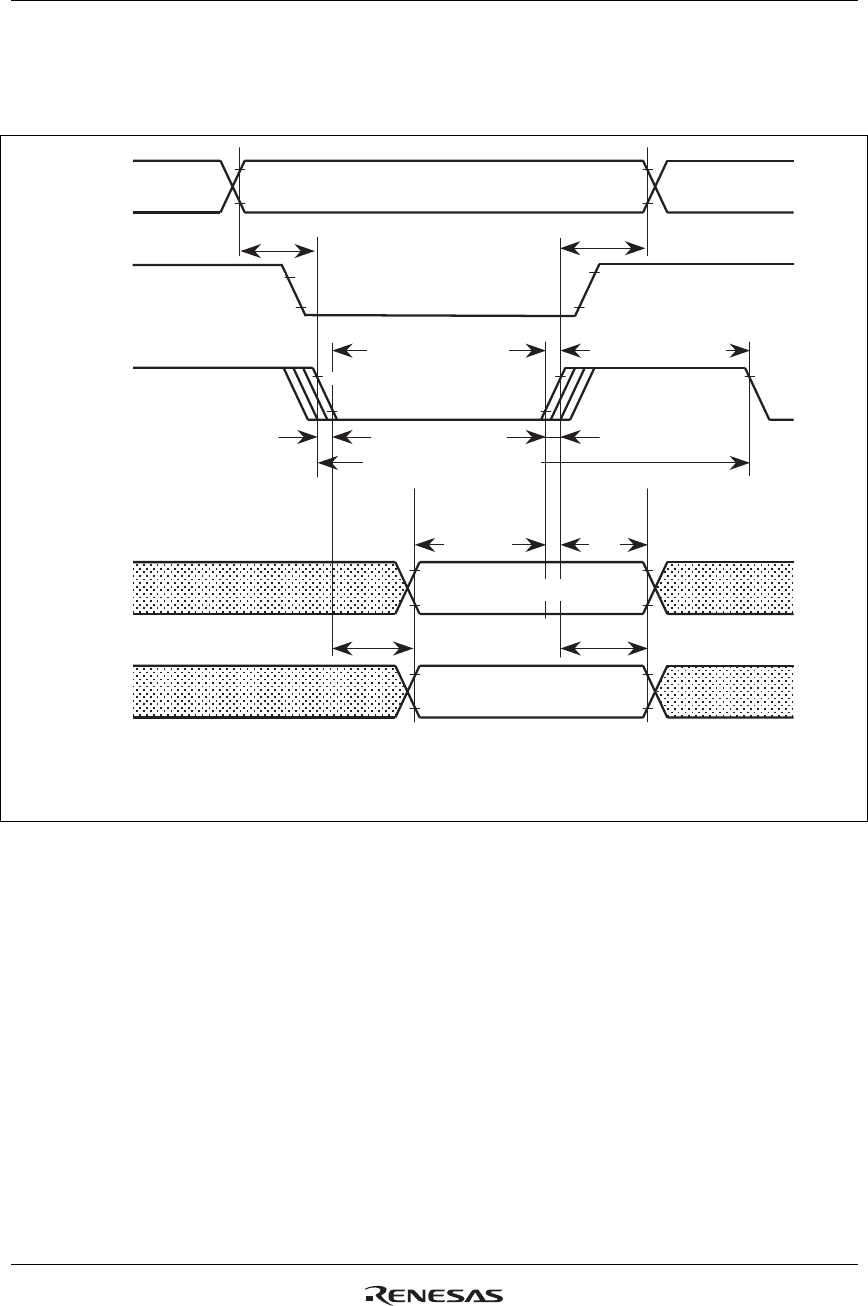

Timing Characteristics

80-system Bus Interface

tDDR tDHR

VIL

VOL

tWRf

VIH

VIL

VIH

VIL

VIL

VIH

VIL

VIHVIH

VIL

VIH

RS

CSX

WRX

RDX

tAS

tAH

PWHW PWHR

tWRr

tCYCW tCYCR

VIH

VIL

DB17-0

VIH

tDSW

tH

VOH

VOL

DB17-0

VOH

PWLW PWLR

VIH

VIL

Note 2

Note 1

Write Data

Read Data

Note 1: PWLW and PWLR are defined by the overlap period when CSX is "Low" and either of WRX or RDX is "Low".

Note 2: Unused DB pins must be fixed at "IOVCC" or "GND".

Note 2

Figure A 80-system Bus Interface