R61509V Target Spec

Rev. 0.11 April 25, 2008, page 173 of 181

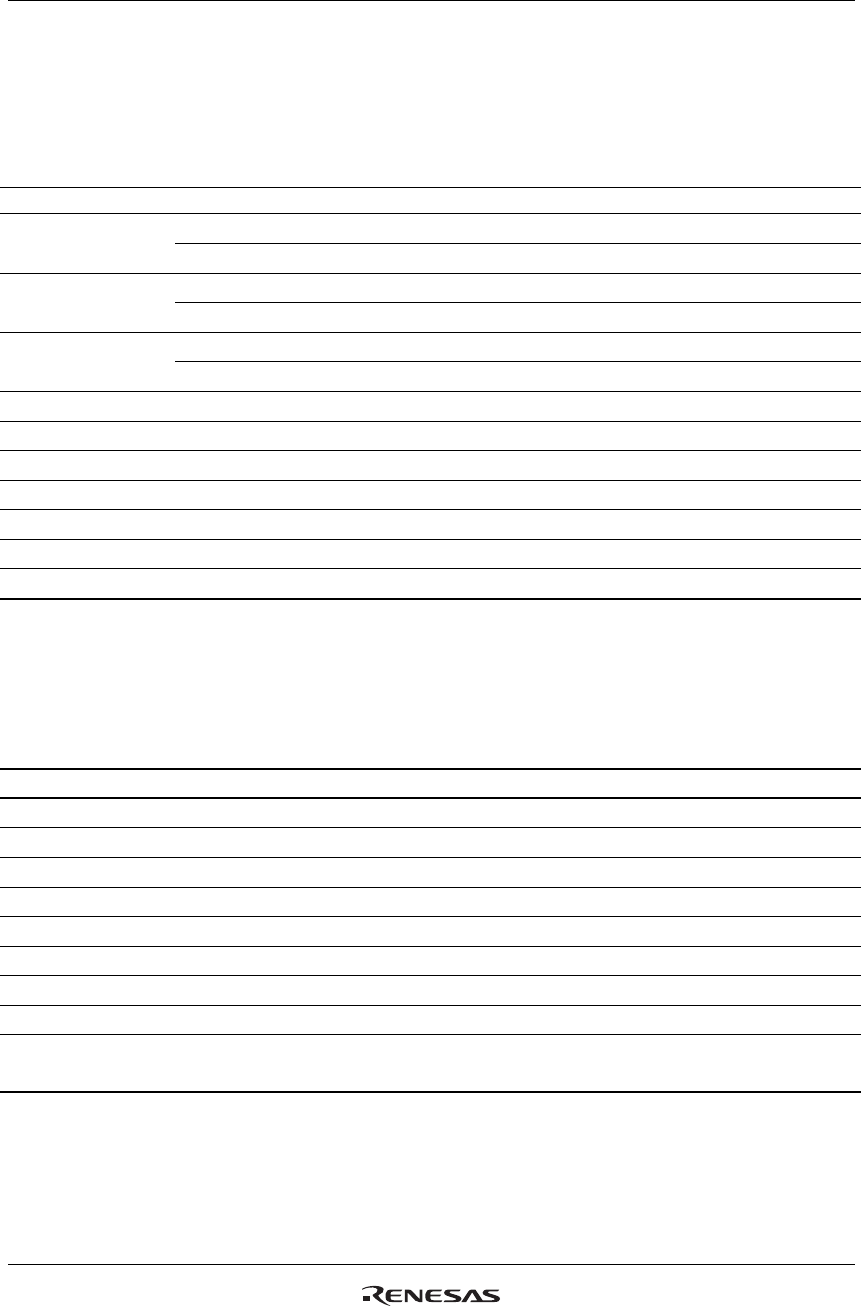

Clock Synchronous Serial Interface Timing Characteristics

(IOVCC=1.65V~3.30V) TBD

Table 90

Item Symbol Unit Test condition Min. Typ. Max.

Write (receive) tSCYC ns Figure B 100

(TBD)

- 20,000

Serial clock cycle

time

Read (transmit) t

SCYC ns Figure B 350

(TBD)

- 20,000

Write (receive) tSCH ns Figure B 40

(TBD)

- -

Serial clock

high-level width

Read (transmit) t

SCH ns Figure B 150

(TBD)

- -

Write (receive) tSCL ns Figure B 40

(TBD)

- -

Serial clock

low-level width

Read (transmit) t

SCL ns Figure B 150

(TBD)

- -

Serial clock rise/fall time tSCr,tSCf ns Figure B - - 15

(TBD)

Chip select setup time tCSU ns Figure B 20

(TBD)

- -

Chip select hold time tCH ns Figure B 60

(TBD)

- -

Serial input data setup time tSISU ns Figure B 30

(TBD)

- -

Serial input data hold time tSIH ns Figure B 30

(TBD)

- -

Serial output data delay time tSOD ns Figure B - - 130

(TBD)

Serial output data delay time tSOH ns Figure B 5

(TBD)

- -

RGB Interface Timing Characteristics

(18-/16-bit RGB interface, IOVCC=1.65V~3.30V) TBD

Table 91

Item Symbol Unit Test condition Min. Typ. Max.

VSYNC/HSYNC setup time tSYNCS clock Figure D 0.5

(TBD)

- 1.5

ENABLE setup time tENS ns Figure D 10

(TBD)

- -

ENABLE hold time tENH ns Figure D 20

(TBD)

- -

DOTCLK low-level pulse width PWDL ns Figure D 40

(TBD)

- -

DOTCLK high-level pulse width PWDH ns Figure D 40

(TBD)

- -

DOTCLK cycle time tCYCD ns Figure D 100

(TBD)

- -

Data setup time tPDS ns Figure D 10

(TBD)

- -

Data hold time tPDH ns Figure D 40

(TBD)

- -

DOTCLK, VSYNCX and HSYNCX

rise/fall time

trgbr

,

trgbf

ns Figure D

- -

15