R61509V Target Spec

Rev. 0.11 April 25, 2008, page 14 of 181

Pin Function

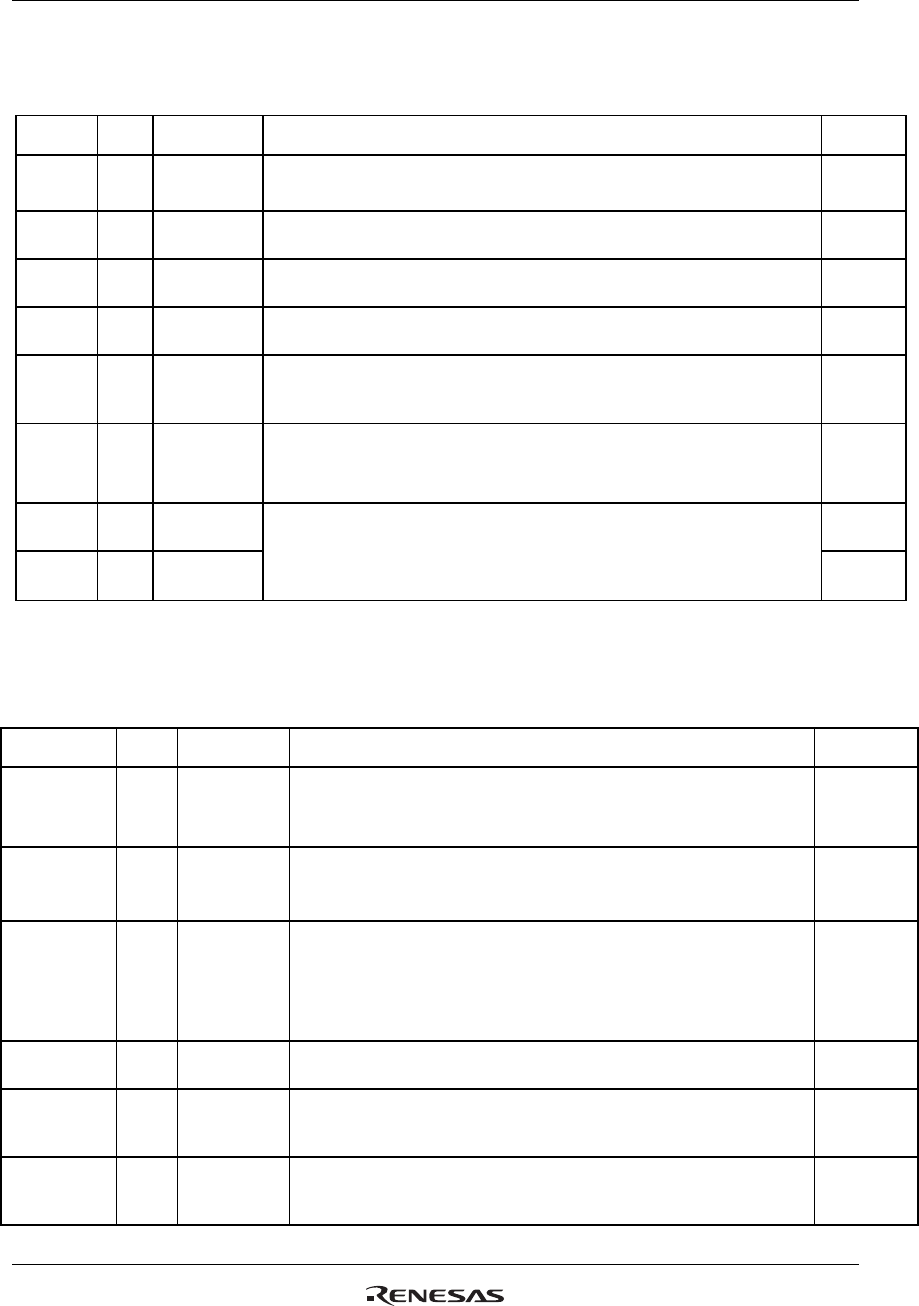

Table 5 External Power Supply

Signal I/O Connect to Function

When not

used

VCC I

Power

supply

Power supply for Internal VDD regulator.

VCC

≧

IOVCC

―

IOVCC I

Power

supply

Power supply for interface pins. ―

GND I

Power

supply

GND level for internal logic and interface pins. GND=0V. ―

VCI I

Power

supply

Power supply for liquid crystal power supply analog circuit. ―

VCILVL I

Reference

power

supply

Connect to an external power supply at the same level as VCI the

power supply for liquid crystal power supply analog circuit. In case of

COG, connect to VCI on the FPC to prevent noise.

―

AGND I

Power

supply

Analog GND (for logic regulator and liquid crystal power supply).

AGND = 0V.

In case of COG, connect to GND on the FPC to prevent noise.

―

VPP1 I

Power

supply

Open or

AGND

VPP3A I

Power

supply

Power supply for internal NVM.

See section “NVM Control” for input voltages during write and erase

operation using VPP1-VPP3A pins.

Open or

AGND

Note 1: VCC, GND and AGND pins are allocated several different places on the chip. Make sure to connect

all of them to power following “Connection Example”.

Table 6 Bus Interface (Amplitude: IOVCC~GND)

Signal I/O Connect to Function

When not

used

CSX I

Host

processor

Chip selection signal. (Amplitude: IOVCC-GND)

Low: The R61509V is selected and accessible.

High: The R61509V is not selected and not accessible.

IOVCC

RS I

Host

processor

Register selection signal. (Amplitude: IOVCC-GND)

Low: Index register is selected.

High: Control register is selected.

IOVCC

WRX_SCL I

Host

processor

Write strobe signal when 80-system bus interface is selected.

Data are written when Low level.

Synchronous clock signal when clock synchronous serial

interface is selected.

(Amplitude: IOVCC-GND)

IOVCC

RDX I

Host

processor

Read strobe signal when 80-system bus interface is selected.

Data are read when Low level. (Amplitude: IOVCC-GND)

IOVCC

SDI I

Host

processor

Serial data input pin when clock synchronous serial interface is

selected. Data are inputted on the rising edge of SCL signal.

(Amplitude: IOVCC-GND)

GND

/IOVCC

SDO O

Host

processor

Serial data output pin when clock synchronous serial interface is

selected. Data are outputted on the falling edge of SCL signal.

(Amplitude: IOVCC-GND)

Open