R61509V Target Spec

Rev. 0.11 April 25, 2008, page 128 of 181

Notes to RGB Interface Operation

1. The following functions are not available in RGB interface operation.

Table 64 Functions Not Available in RGB Interface operation

Function RGB Interface Internal Display Operation

Partial display Not available Available

Scroll function Not available Available

2. The VSYNCX, HSYNCX, and DOTCLK signals must be supplied during display period.

3. The reference clock to generate liquid crystal panel controlling signals in RGB interface operation is

DOTCLK, not the internal clock generated from the internal oscillator.

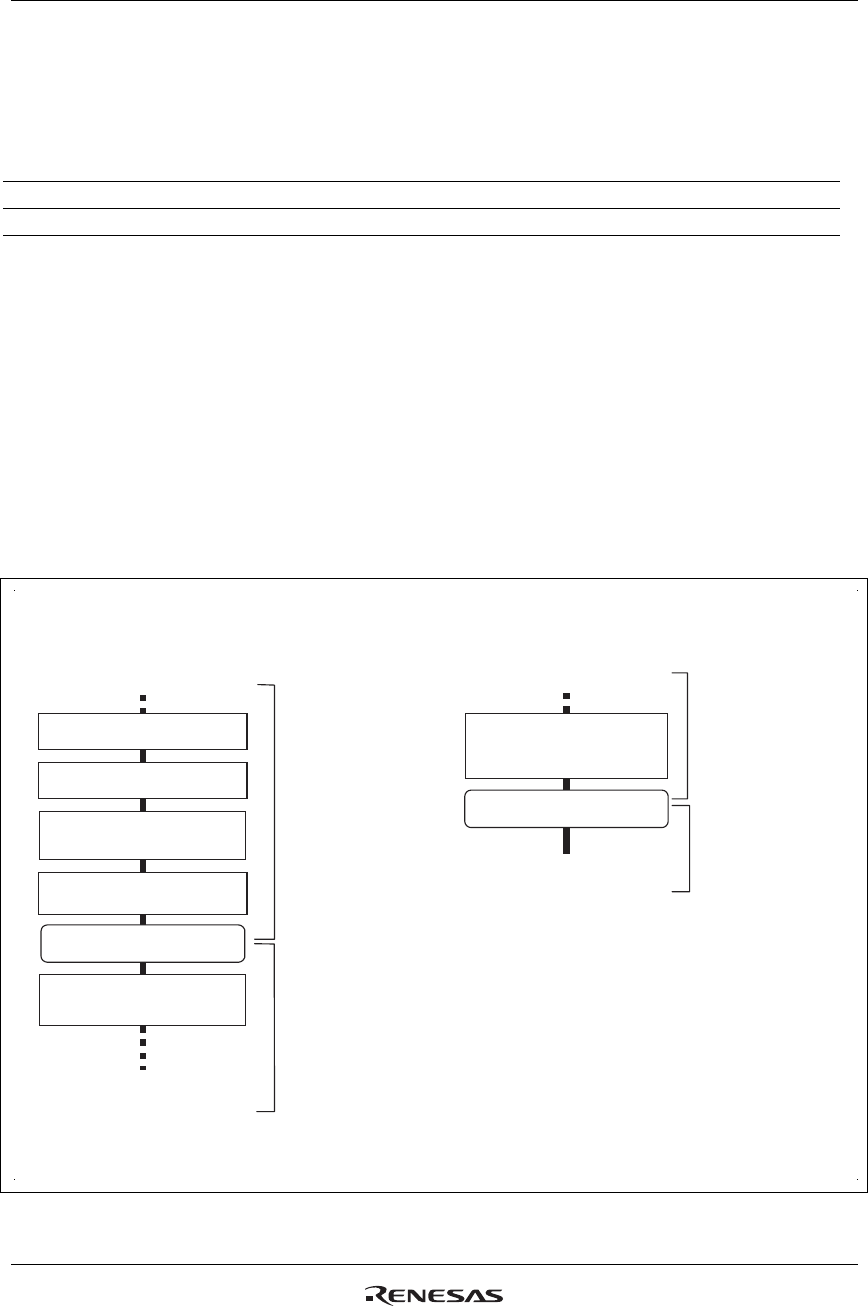

4. When switching between the internal operation mode and the external display interface operation mode,

follow the sequences below in setting instruction.

5. In RGB interface operation, front porch period continues after the end of frame period until next

VSYNCX input is detected.

6. RGB and 80-system bus interfaces cannot be used simultaneously.

7. In RGB interface operation, RAM address AD16-0 is set in the address counter every frame on the

falling edge of VSYNCX.

Internal Clock Operation to RGB Interface (1)

Operation via RGB interface

RGB Interface (1) to Internal Clock Operation

Internal clock operation

AM = 0

RAM address set

Set DM1-0 = 01 and RM = 1

for RGB interface

Write data to RAM

via RGB interface

Wait one frame period

or more

Set index register to R202h

Display operation in

synchronization with

internal clocks

RGB interface operation

Display operation in

synchronization with

VSYNCX, HSYNCX, and

DOTCLK

Display operation in

synchronization with VSYNCX,

HSYNCX, and DOTCLK

Internal clock operation

Set internal clock

operation mode*

(DM1-0 = 00 and RM = 0)

Display operation in

synchronization with

internal clocks

Note: Continue RGB interface signals at least for

one frame period after setting DM1-0, RM bits

to internal clock operation.

Note: Input the RGB interface signals before setting the DM1-0 and RM bits

to the RGB interface operation.

*Instruction setting for

the RGB interface operation

is enebled from the next frame period.

*Instruction setting to the

internal clock operation

is enebled from the next

frame period.

Wait one frame period

or more

Figure 49 RGB and Internal Clock Operation Mode Switching Sequences