R61509V Target Spec

Rev. 0.11 April 25, 2008, page 157 of 181

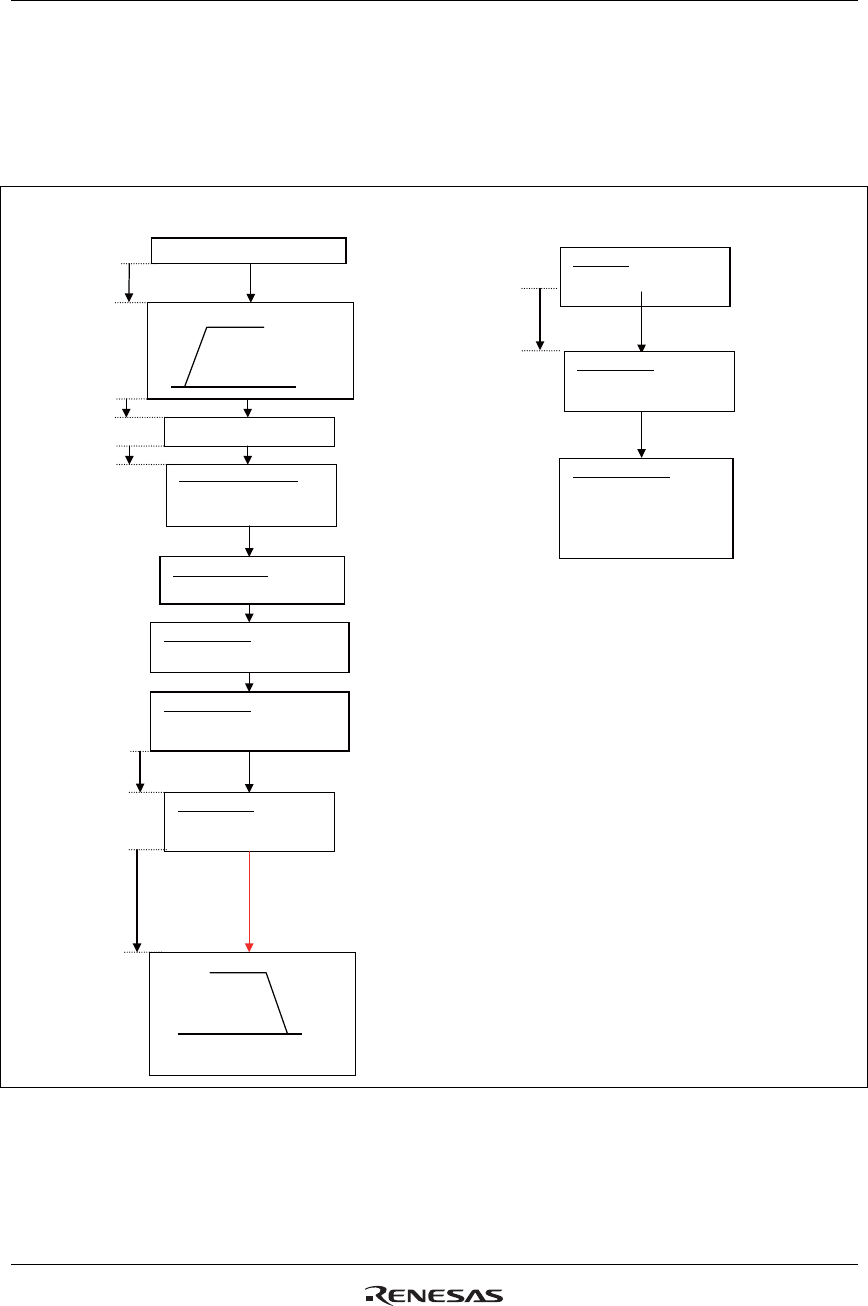

NVM Write Sequence

Defined 16 bit data is written to the selected address. When “0” is written to these bits, the bits are set to

“0”. If the data is erased from the bit, the bit is returned to ”1”. The bit to which data is not written should

be set to “1”.

RS=0, DB=16’h0000

RS=0, DB=16’h0000

RS=0, DB=16’h0000

R

S

=

0,

DB=1

6

’h

0000

R6F1:16’h****

R6F0:16’h0010

(TE=0,CALB=0,EOP=2’h1)

R6F0:16’h0090

(TE=1,CALB=0,EOP=2’h1)

150msr50ms(TBD)

GND

VPP1=

9

.2r

0

.

3

V

VPP3A/VPP3B=GND

GND

VPP1

=

9.2

r

0.3

V

VPP3A =GND

6F0h:16’h0040

(CALB=1)

NVM Write Sequence

NVM Load (Register Resetting) Sequence

1ms

or more

Power ON reset

Transfer synchronization

2msec

or more

1msec

or more

1msec

or more

NVM write setting

NVM write start

NVM write end

Power supply (VCC, VCI, IOVCC) ON

NVM write data set

1us

or more

(NVDAT=16’hXX (arbitrary data))

RA0: 16’h0000

(TE=0, EOP=2’h0,

NVAD=2’h0)

NVM load end

NVM load

(Automatically CALB = 0)

NVM data read

R280h: VCM[6:0], UID[7:0]

Instruction read

Figure 67 NVM Write Sequence