R61509V Target Spec

Rev. 0.11 April 25, 2008, page 103 of 181

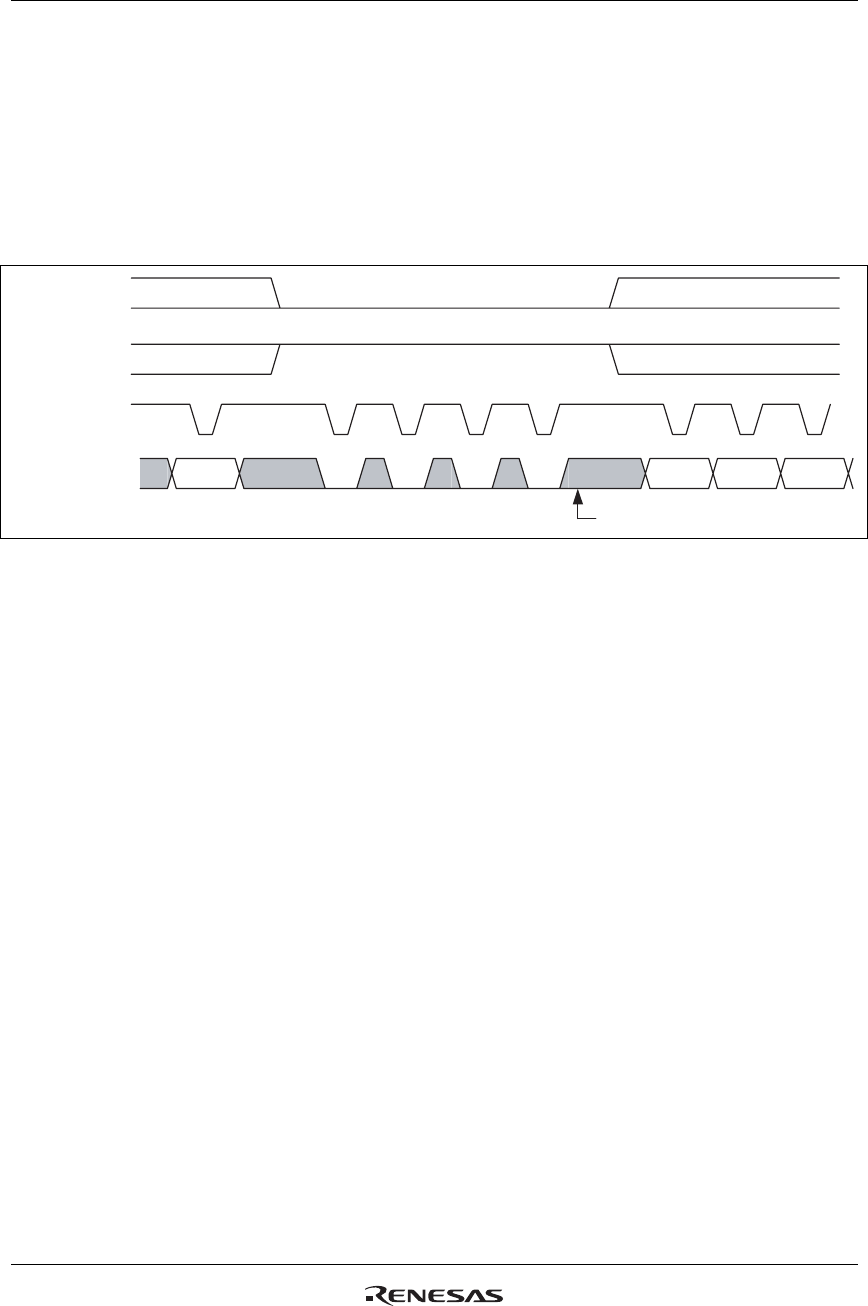

Data Transfer Synchronization in 16-bit Bus Interface Operation

The R61509V supports data transfer synchronization function to reset the counters for upper 16-/2-bit and

lower 2-/16-bit transfers in 16-bit 2-transfer mode. When a mismatch occurs in upper and lower data

transfers due to noise and so on, the 000H instruction is written four times consecutively to reset the upper

and lower counters in order to restart the data transfer from upper 2/16 bits. The data transfer

synchronization, when executed periodically, can help the display system recover from runaway.

Make sure to execute data transfer synchronization after reset operation before transferring instruction.

WRX

RDX

RS

(16-bit transfer synchronization)

DB17 ~ DB10,

DB8 ~ DB1

Upper

Lower

Upper UpperLower

"000"H"000"H"000"H"000"H

Figure 21 16-bit Data Transfer Synchronization