R61509V Target Spec

Rev. 0.11 April 25, 2008, page 118 of 181

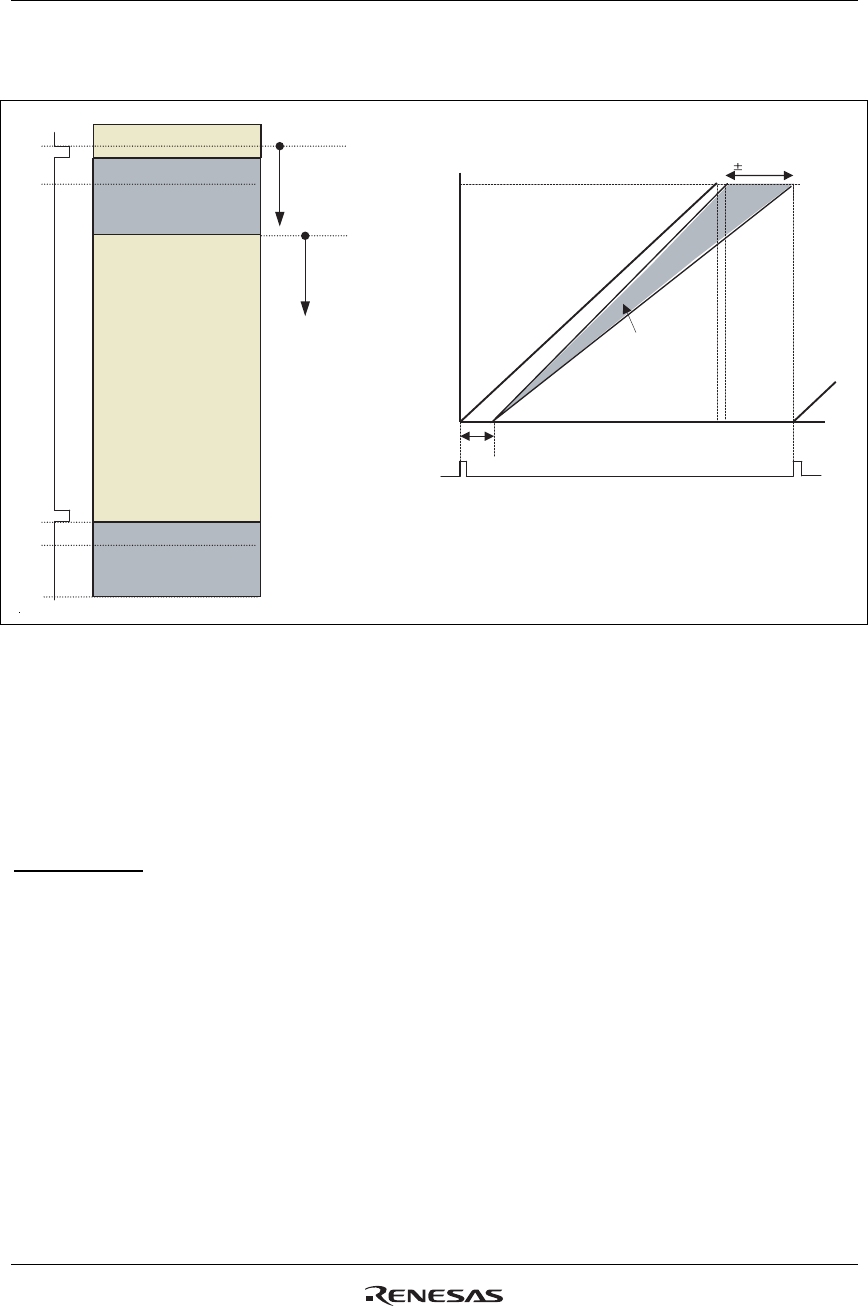

starts the display operation of the data written in that line and can write moving picture data without

causing flicker on the display.

7%

FP+BP=16H

432

0

FMARK

16.67

(60Hz)

[ms]

FMARK

RAM

write

Display

operation

Back porch (14 lines)

Main panel

Moving picture

display

(432 lines)

Front porch (2 lines)

RC oscillation

Display

operation

[line]

RAM write

7.4MHz

Line processing

Back porch (14 lines)

Front porch (2 lines)

Figure 40

Note to display operation synchronous data transfer using FMARK signal

The above example of calculation gives a theoretical value. Possible causes of variances of internal

oscillator should be taken into consideration. Make enough margin in setting RAM write speed for

this operation.

FMP bit setting

The microcomputer detects FMARK signal outputted at the position defined by FMP bit. The R61509V

outputs an FMARK pulse when the R61509V is driving the line specified by FMP bits. The FMARK

signal can be used as a trigger signal to write display data in synchronization with display operation by

detecting the address where data is read out for display operation.

The FMARK output interval is set by FMI bits. Set FMI bits in accordance with display data rewrite cycle

and data transfer rate.