R61509V Target Spec

Rev. 0.11 April 25, 2008, page 69 of 181

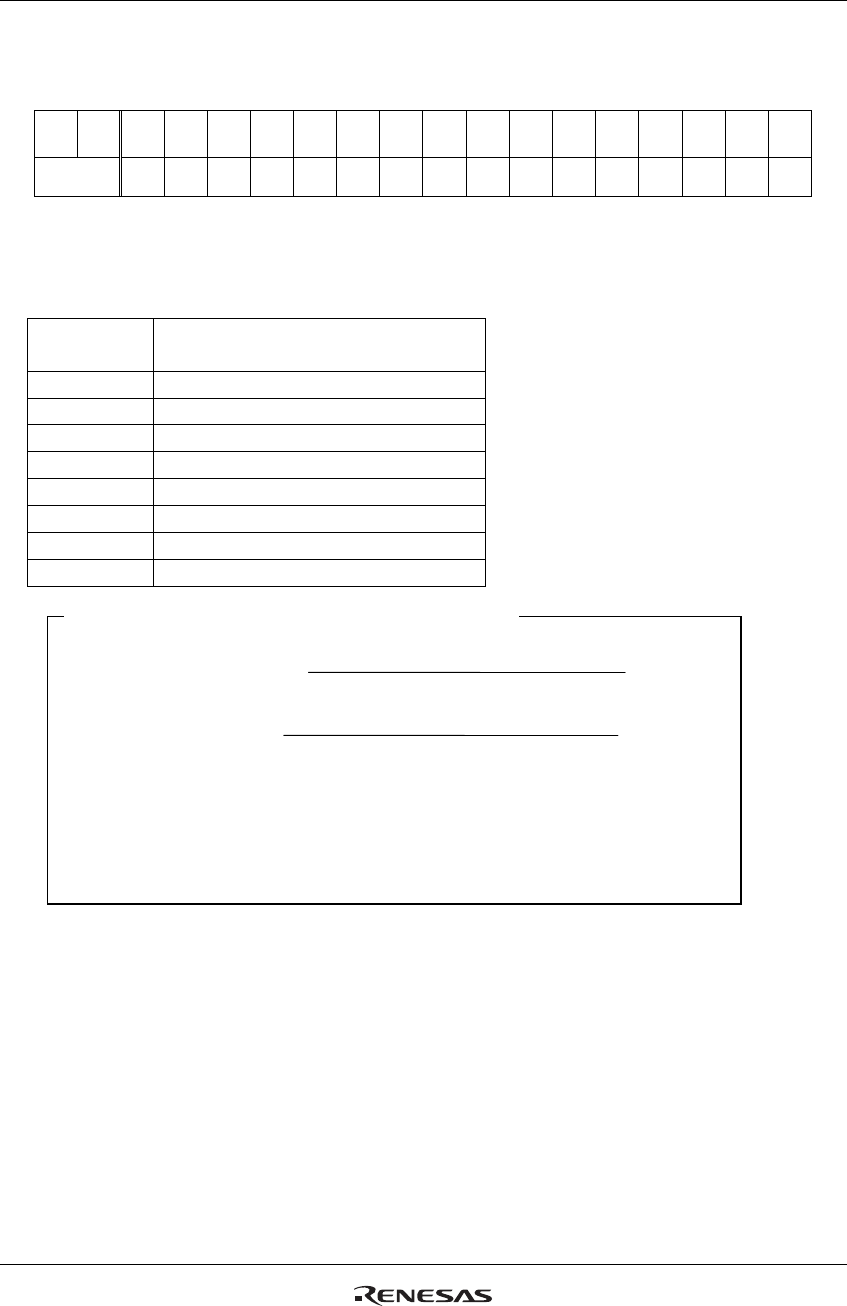

Power Control 2 (R101h)

DC1 [2:0]: Sets step-up clock frequency for Step-up Circuit 2. The step-up clock is in synchronization

with internal clock.

Table 42 Step-up Frequency (Step-up Circuit 1)

DC1[2:0]

Step-up Circuit 2

Step-up frequency (fDCDC2)

3’h0 Step-up Circuit 2 halts

3’h1 Setting inhibited

3’h2 Line frequency / 4

3’h3 Line frequency / 8

3’h4 Line frequency / 16

3’h5 Setting inhibited

3’h6 Setting inhibited

3’h7 Setting inhibited

R/W RS IB15 IB14 IB13 IB12 IB11 IB10 IB9 IB8 IB7 IB6 IB5 IB4 IB3 IB2 IB1 IB0

R/W 1 0 0 0 0 0

DC1

[2]

DC1

[1]

DC1

[0]

0

DC0

[2]

DC0

[1]

DC0

[0]

0

VC

[2]

VC

[1]

VC

[0]

Default 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1

fosc : Internal clock frequency

N

umber of clock per line : RTN*[4:0] (RTNI or RTNE)

Division ratio : DIV*[1:0] (DIVI or DIVE)

N

: DC1 [2:0]

Step-up clock frequency

(f

DCDC2

)

=

Internal clock frequency f

OSC

[

Hz

]

[Step-up clock frequency for Step-up Circuit 2]

Number of clock per line x Division ratio x 2

(N)

Line fre

q

uenc

y

2

(N)

=

[

Hz

]