R61509V Target Spec

Rev. 0.11 April 25, 2008, page 15 of 181

DB[17:0] I/O

Host

processor

18-bit parallel bi-directional data bus for 80-system interface

operation (Amplitude: IOVCC-GND).

8-bit I/F: DB17-DB10 are used.

9-bit I/F: DB17-DB9 are used.

16-bit I/F: DB17-DB10 and DB8-1 are used.

18-bit I/F: DB17-DB0 are used.

18-bit parallel bi-directional data bus for RGB interface operation

(Amplitude: IOVCC-GND).

16-bit I/F: DB17-DB13 and DB11-1 are used.

18-bit I/F: DB17-DB0 are used.

GND /

IOVCC

ENABLE I

Host

processor

Data enable signal for RGB interface operation.

Low: accessible (selected)

High: Not accessible (Not selected)

The polarity of ENABLE signal can be inverted by setting the

EPL bit. (Amplitude: IOVCC-GND).

GND /

IOVCC

VSYNCX I

Host

processor

Frame synchronous signal. Low active. (Amplitude: IOVCC-

GND).

GND /

IOVCC

HSYNCX I

Host

processor

Line synchronous signal, Low active. (Amplitude: IOVCC-GND)

GND /

IOVCC

DOTCLK I

Host

processor

Dot clock signal. Data is input on the rising edge of DOTCLK.

(Amplitude: IOVCC-GND)

GND /

IOVCC

FMARK O

Host

processor

Frame head pulse. (Amplitude: IOVCC-GND)

FMARK is used when writing data to the internal RAM.

Open

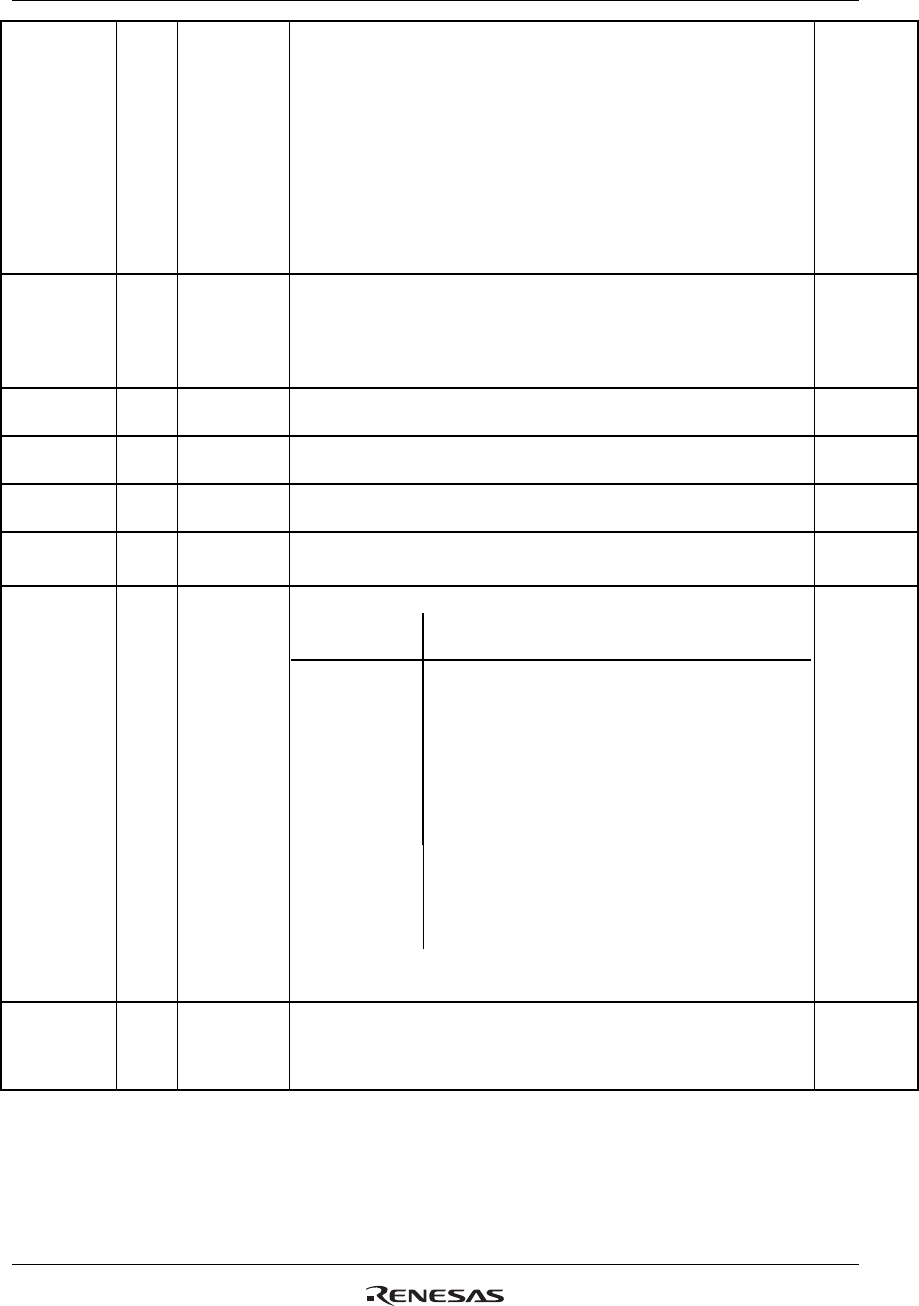

IM2-1,

IM0_ID

I

GND /

IOVCC

Select host processor interface. (Amplitude: IOVCC-GND)

IM2 IM1

IM0

System Interface

DB pins

in use

Colors

0 0 0

80-system 18-bit

interface

DB17-0 262,144

0 0 1

80-system 9-bit

interface

DB17-9 262,144

0 1 0

80-system 16-bit

interface

DB17-10,

8-1

262,144

(Note 1)

0 1 1

80-system 8-bit

interface

DB17-10

262,144

(Note 2)

1 0

*

(ID)

Clock synchronous

serial interface

― 65536

1 1 0 Setting inhibited ― ―

1 1 1 Setting inhibited

―

―

Note 1: 65,536 colors in one-transfer operation.

Note 2: 65,536 colors in two-transfer operation.

―

RESETX I

Host

processor

or external

RC circuit

Reset pin. The R61509V is reset when RESETX is low. Make

sure to execute a power on reset after turning power on.

(Amplitude: IOVCC-GND)

―