www.ti.com

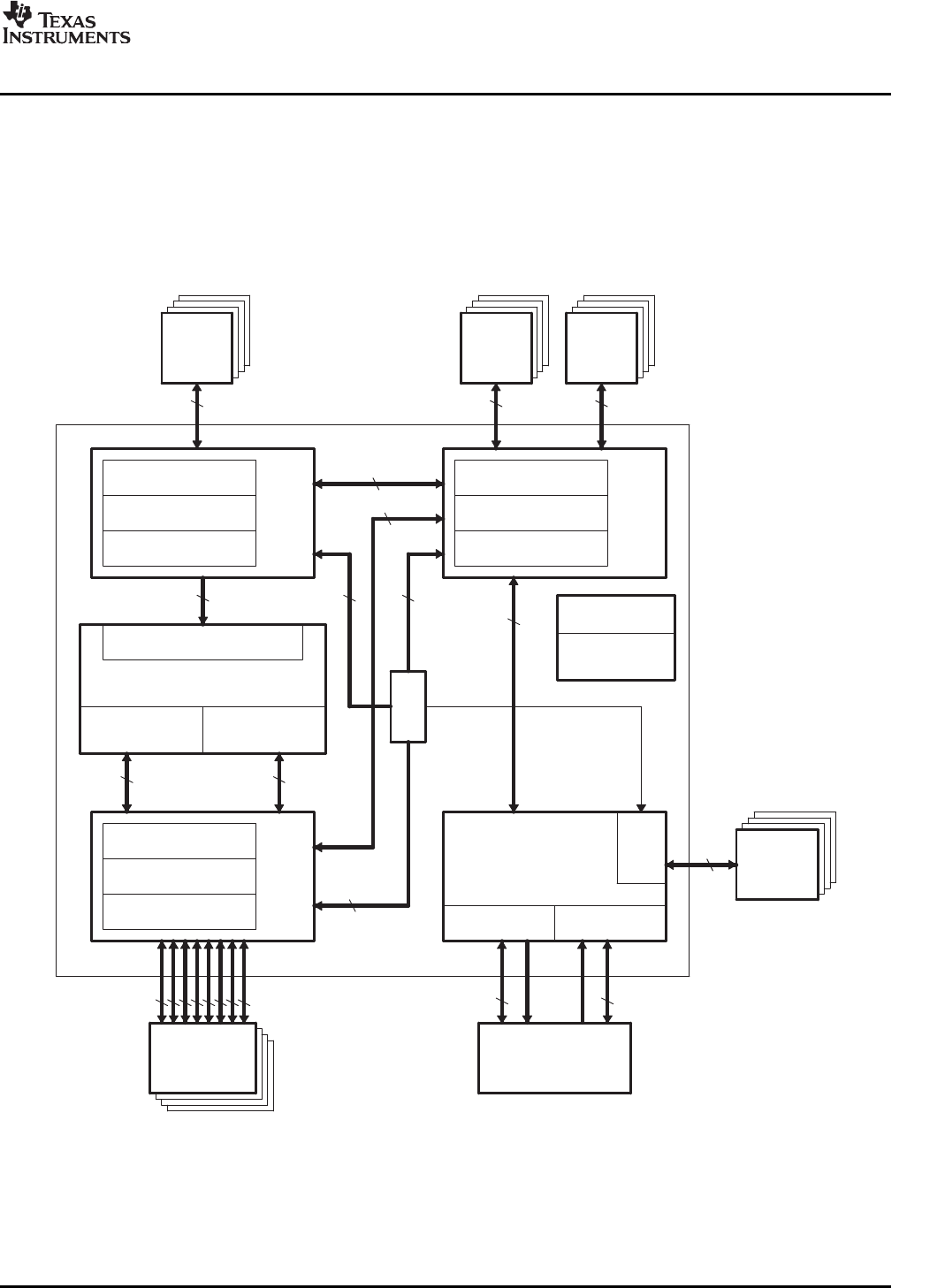

Cache control

Memory protect

Bandwidth mgmt

L1P

RAM/

cache

256

Bandwidth mgmt

Memory protect

Cache control

256

L2

256

RAM/

Cache

ROM

256

Instruction fetch

file A file B

C64x+ CPU

256

Cache control

Memory protect

Bandwidth mgmt

L1D

128 128

8 x 32

IDMA

256

256

128

256

Power down

Interrupt

controller

CFG

MDMA SDMA

EMC

256

32

Chip

registers

64 64

RAM/

cache

Register Register

System

infrastructure

TMS320C64x+CPU

•Protectedmodeoperation:atwo-levelsystemofprivilegedprogramexecutiontosupporthigher

capabilityoperatingsystemsandsystemfeatures,suchasmemoryprotection

•Exceptionssupportforerrordetectionandprogramredirectiontoproviderobustcodeexecution

•Hardwaresupportformoduloloopoperationtoreducecodesize

•Industry'sfirstassemblyoptimizerforrapiddevelopmentandimprovedparallelization

Figure2-1.TMS320C64x+MegamoduleBlockDiagram

SPRU978E–March2008TMS320C64x+Megamodule17

SubmitDocumentationFeedback