www.ti.com

5.4.15ClockStatusRegister(CKSTAT)

PLLControllerRegisters

Theclockstatusregister(CKSTAT)isshowninFigure5-17anddescribedinTable5-19.CKSTATshows

clockstatusforallclocks,exceptSYSCLKn.

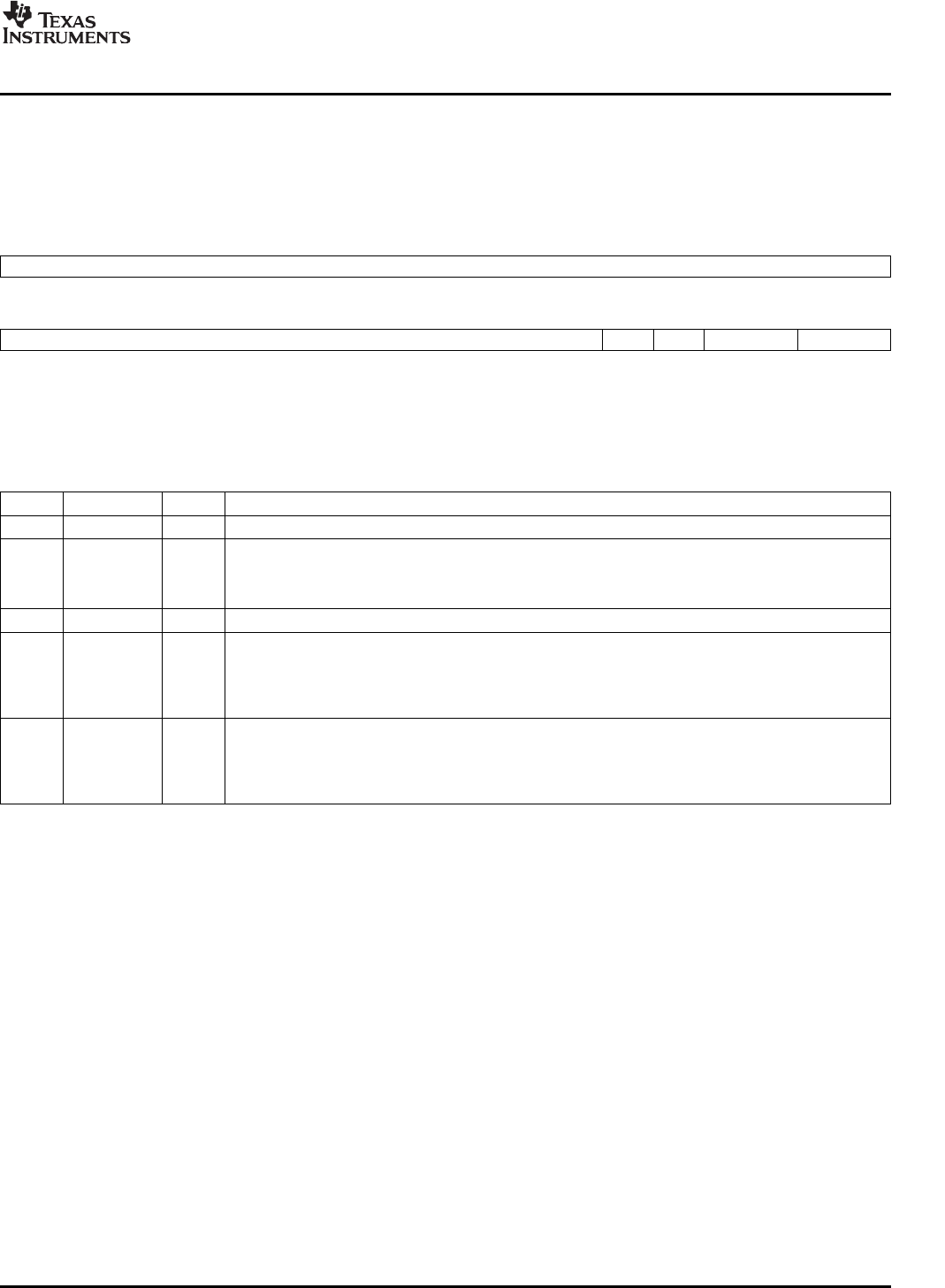

Figure5-17.ClockStatusRegister(CKSTAT)

3116

Reserved

R-0

1543210

ReservedBPONRsvdOBSONAUXON

R-0R-1R-0R-0or1

(1)

R-0or1

(2)

LEGEND:R=Readonly;-n=valueafterreset

(1)

ForPLLC1,OBSONdefaultsto1;forPLLC2,OBSONisreservedanddefaultsto0.

(2)

ForPLLC1,AUXONdefaultsto1;forPLLC2,AUXONisreservedanddefaultsto0.

Table5-19.ClockStatusRegister(CKSTAT)FieldDescriptions

BitFieldValueDescription

31-4Reserved0Reserved

3BPONSYSCLKBPonstatus.SYSCLKBPiscontrolledinthebypassdividerregister(BPDIV).

0SYSCLKBPisoff.

1SYSCLKBPison.

2Reserved0Reserved

1OBSONOBSCLKonstatus.OBSCLKiscontrolledintheoscillatordivider1register(OSCDIV1)andbythe

OBSENbitintheclockenablecontrolregister(CKEN).NotapplicableonPLLC2(thisbitisreserved).

0OBSCLKisoff.

1OBSCLKison.

0AUXONAUXCLKonstatus.AUXCLKiscontrolledbytheAUXENbitintheclockenablecontrolregister

(CKEN).NotapplicableonPLLC2(thisbitisreserved).

0AUXCLKisoff.

1AUXCLKison.

SPRU978E–March2008PLLController59

SubmitDocumentationFeedback