www.ti.com

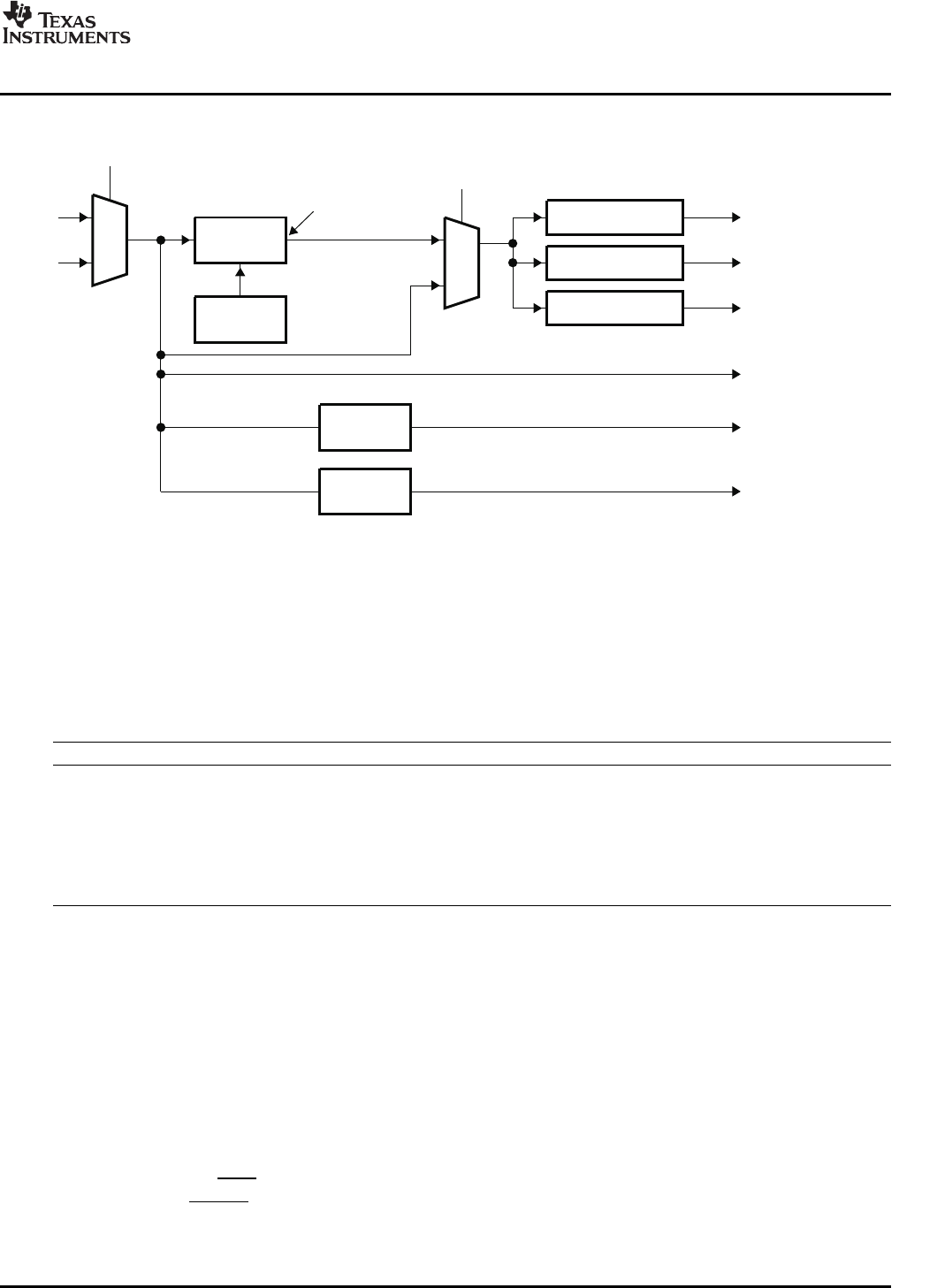

PLLDIV1(/1)

PLLDIV3(/6)

PLLDIV2(/3)

SYSCLK1

(CLKDIV1Domain)

SYSCLK3

(CLKDIV6Domain)

SYSCLK2

(CLKDIV3Domain)

1

0

PLLM

PLL

0

1

BPDIV

CLKMODE

CLKIN

OSCIN

PLLEN

SYSCLKBP

(VPSS-VPBR

ClockSource)

OBSCLK

(CLKOUT0Pin)

PLLOUT

AUXCLK

(CLKINDomain)

OSCDIV1

5.2.1DeviceClockGeneration

5.2.2StepsforChangingPLL1/CoreDomainFrequency

PLL1Control

Figure5-1.PLL1StructureintheTMS320DM643xDMP

PLLC1generatesseveralclocksfromthePLL1outputclockforusebythevariousprocessorsand

modules.ThesearesummarizedinTable5-1.SYSCLK1,SYSCLK2,andSYSCLK3mustmaintainafixed

frequencyratiorequirement,nomatterwhatreferenceclock(PLLorbypass)orPLLfrequencyisused.

Table5-1.SystemPLLC1OutputClocks

PLLC1OutputClockUsedbyDefaultDivider

SYSCLK1DSPSubsystem/1

SYSCLK2SCR,EDMA,VPSS,CLKDIV3Domainperipherals/3

SYSCLK3CLKDIV6Domainperipherals/6

AUXCLKCLKINDomainperipheralsNA

OBSCLKCLKOUT0source/1

SYSCLKBPVPBEclocksource/1

RefertotheappropriatesubsectiononhowtoprogramthePLL1/CoreDomainclocks:

•IfthePLLispowereddown(PLLPWRDNbitinPLLCTLissetto1),followthefullPLLinitialization

procedureinSection5.2.2.1toinitializethePLL.

•IfthePLLisnotpowereddown(PLLPWRDNbitinPLLCTLisclearedto0),followthesequencein

Section5.2.2.2tochangethePLLmultiplier.

•IfthePLLisalreadyrunningatadesiredmultiplierandyouonlywanttochangetheSYSCLKdividers,

followthesequenceinSection5.2.2.3.

NotethatthePLLispowereddownafterthefollowingdevice-levelglobalresets:

•Power-onReset(POR)

•WarmReset(RESET)

•MaxReset

SPRU978E–March2008PLLController39

SubmitDocumentationFeedback