www.ti.com

4.2.5VideoProcessingBackEnd

3

2

0

1

0

1

2

PLLDIV2

CLK54

PLL2

DDR_CLKx2

PCLK

VPBECLK

MXI

CLK_VENC

CLK_DAC

1

0

venc_sclk_enc

CG OSD

VENC

DACs

venc_div2

venc_sclk_osd

VPSS

VPSS_CLKCTL.MUXSEL

CLK54 CLK_VENC CLK_DAC

0 27 MHzOff 27 MHz

1h 54 54 MHz 54 MHz

2h Off VPBECLK VPBECLK

3h Off PCLK Off

PLLDIV1

PLLC1

SYSCLKBP

VPSS_CLKCTL.MUXSEL

ClockDomains

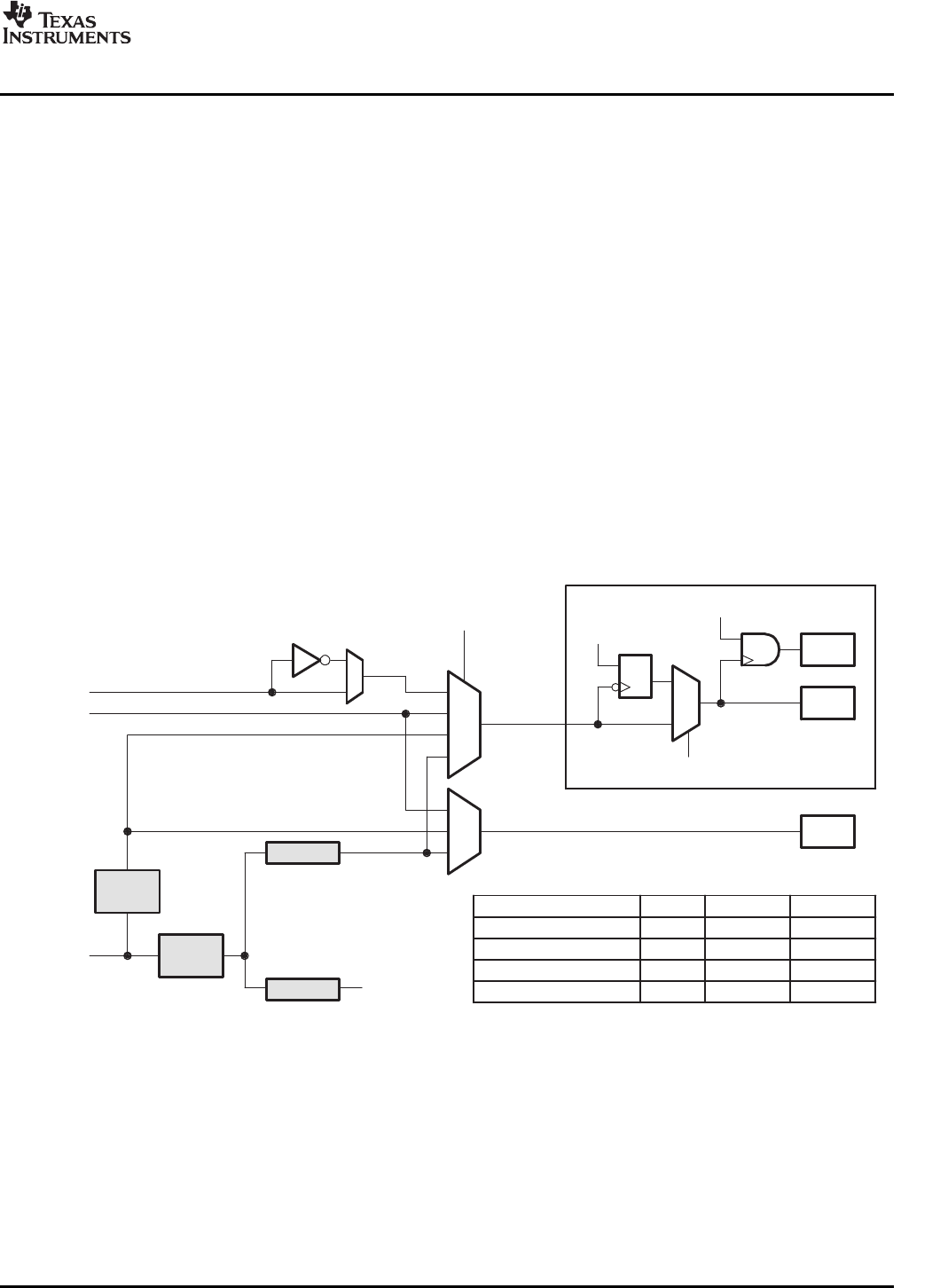

Thevideoprocessingbackend(VPBE)isasubmoduleofthevideoprocessingsubsystem(VPSS).The

VPBEmustinterfacewithavarietyofLCDs,aswellasthe4-channelDACmodule.Therearemany

differenttypesofLCDs,whichrequiremanydifferentspecificfrequencies.Therangeoffrequenciesthat

thepininterfaceneedstorunis6.25MHZto75MHZ.

TherearetwoasynchronousclockdomainsintheVPBE:theexternalclockdomain(6.25MHZto75

MHZ)andtheinternal(system)clockdomain,whichisattheDSP÷3clockrate.

Theexternalclockdomaincangetitsclockfrom4sources:

•PLLC1SYSCLKBP(typically27MHZ,MXI/CLKINdivideby1)

•TheVPBECLKinputpin

•TheVPFEpixelclockinput(PCLK)

•PLLC2SYSCLK2(adividedownfromPLL2)

The4DACsarehookeduptotheVENCmodulethatisintheVPBE.ThedataflowbetweentheVPBE

andDACsissynchronous.ThevariouspossibleclockingmodesareshowninFigure4-2anddescribedin

Table4-6.

TheDACscanhavetheirclocksindependentlygatedoffwhentheDACsarenotbeingused.Thisis

describedinChapter7.

Figure4-2.VPBE/DACClocking

SPRU978E–March2008DeviceClocking35

SubmitDocumentationFeedback