www.ti.com

5.4.12PLLControllerClockAlignControlRegister(ALNCTL)

PLLControllerRegisters

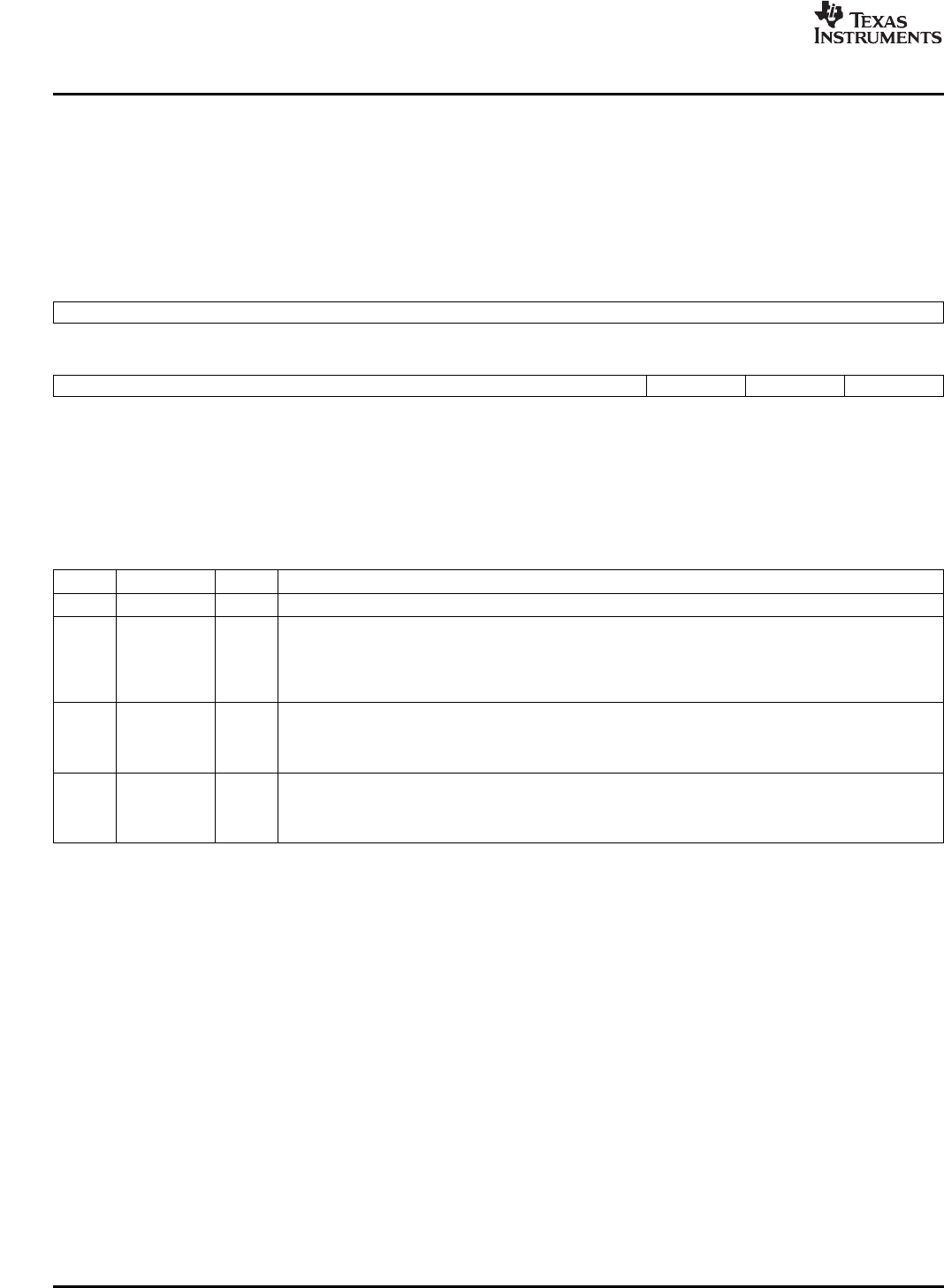

ThePLLcontrollerclockaligncontrolregister(ALNCTL)isshowninFigure5-14anddescribedin

Table5-16.ALNCTLindicateswhichSYSCLKsneedtobealignedforproperdeviceoperation.You

shouldnotmodifyALNCTLfromitsdefaultsettings.

Figure5-14.PLLControllerClockAlignControlRegister(ALNCTL)

3116

Reserved

R-0

153210

ReservedALN3ALN2ALN1

R/W-0hor3h

(1)

R/W-0or1

(2)

R/W-0or1

(3)

R/W-0or1

(4)

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

(1)

ForPLLC1,thisreservedfielddefaultsto3h;forPLLC2,thisreservedfielddefaultsto0h.Usermustnotopposethedefaultvalue.

(2)

ForPLLC1,ALN3defaultsto1;forPLLC2,ALN3isreservedanddefaultsto0.

(3)

ForPLLC1,ALN2defaultsto1;forPLLC2,ALN2defaultsto0.

(4)

ForPLLC1,ALN1defaultsto1;forPLLC2,ALN1defaultsto0.

Table5-16.PLLControllerClockAlignControlRegister(ALNCTL)FieldDescriptions

BitFieldValueDescription

31-3Reserved0or3Reserved.Usermustnotopposethedefaultvalue.

2ALN3SYSCLK3needstobealignedtoothersselectedinthisregister.NotapplicableonPLLC2(thisbitis

reserved).

0SYSCLK3doesnotneedtobealigned.

1SYSCLK3doesneedtobealigned.

1ALN2SYSCLK2needstobealignedtoothersselectedinthisregister.

0SYSCLK2doesnotneedtobealigned.

1SYSCLK2doesneedtobealigned.

0ALN1SYSCLK1needstobealignedtoothersselectedinthisregister.

0SYSCLK1doesnotneedtobealigned.

1SYSCLK1doesneedtobealigned.

56PLLControllerSPRU978E–March2008

SubmitDocumentationFeedback