www.ti.com

5.4PLLControllerRegisters

PLLControllerRegisters

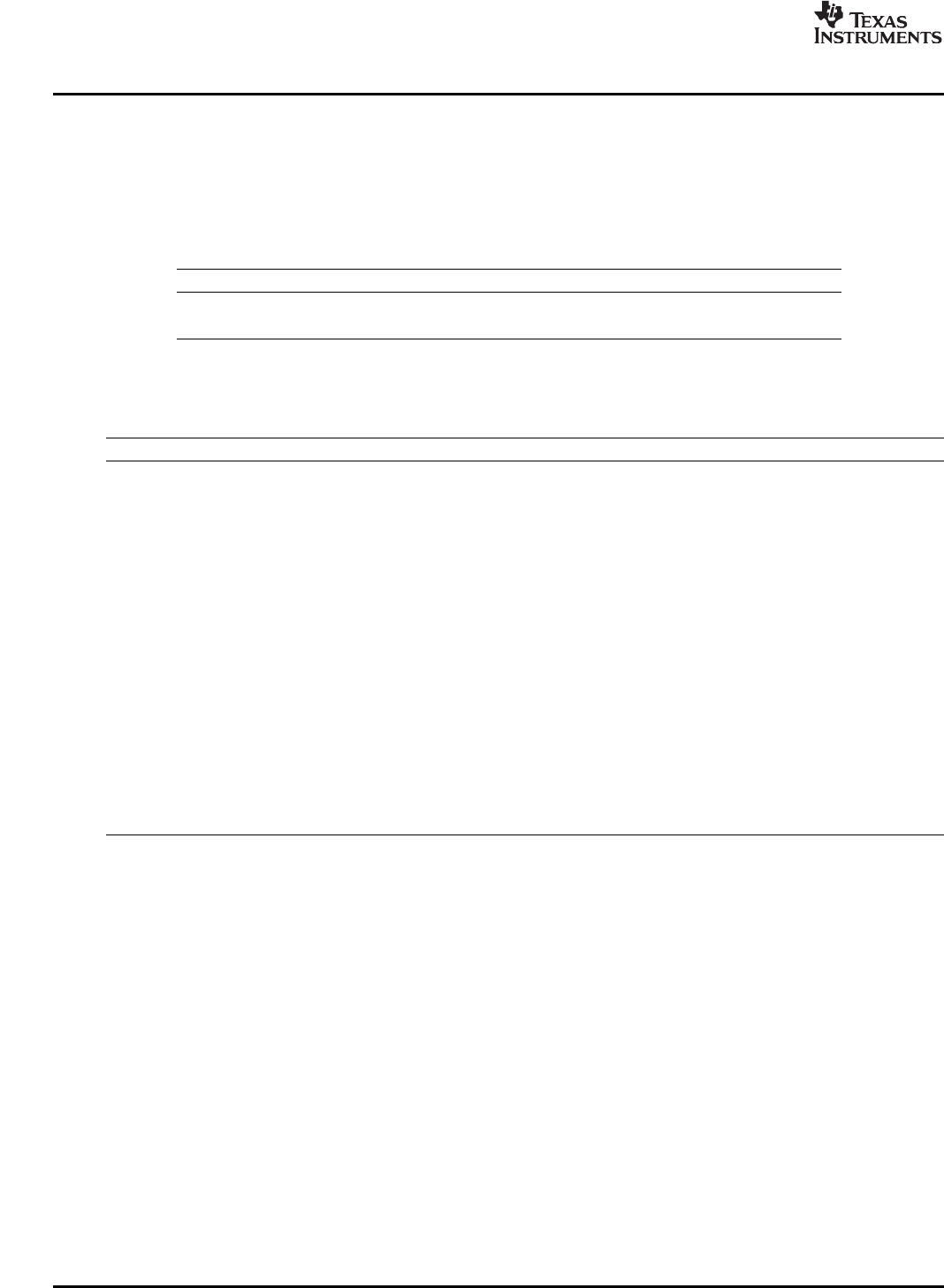

Table5-3liststhebaseaddressandendaddressforthePLLcontrollers.Table5-4liststhe

memory-mappedregistersforthePLLandresetcontroller.Seethedevice-specificdatamanualforthe

memoryaddressoftheseregisters.

Table5-3.PLLandResetControllerList

PLLandResetControllerBaseAddressEndAddressSize

PLLC11C40800h1C40BFFh400h

PLLC21C40C00h1C40FFFh400h

Table5-4.PLLandResetControllerRegisters

OffsetAcronymRegisterDescriptionSection

00hPIDPeripheralIDRegisterSection5.4.1

E4hRSTYPE

(1)

ResetTypeStatusRegisterSection5.4.2

100hPLLCTLPLLControlRegisterSection5.4.3

110hPLLMPLLMultiplierControlRegisterSection5.4.4

118hPLLDIV1PLLControllerDivider1Register(SYSCLK1)Section5.4.5

11ChPLLDIV2PLLControllerDivider2Register(SYSCLK2)Section5.4.6

120hPLLDIV3

(1)

PLLControllerDivider3Register(SYSCLK3)Section5.4.7

124hOSCDIV1

(1)

OscillatorDivider1Register(OBSCLK)Section5.4.8

12ChBPDIVBypassDividerRegisterSection5.4.9

138hPLLCMDPLLControllerCommandRegisterSection5.4.10

13ChPLLSTATPLLControllerStatusRegisterSection5.4.11

140hALNCTLPLLControllerClockAlignControlRegisterSection5.4.12

144hDCHANGEPLLDIVRatioChangeStatusRegisterSection5.4.13

148hCKEN

(1)

ClockEnableControlRegisterSection5.4.14

14ChCKSTATClockStatusRegisterSection5.4.15

150hSYSTATSYSCLKStatusRegisterSection5.4.16

(1)

notsupportedforPLL2.

48PLLControllerSPRU978E–March2008

SubmitDocumentationFeedback