www.ti.com

5.4.8OscillatorDivider1Register(OSCDIV1)

PLLControllerRegisters

Theoscillatordivider1register(OSCDIV1)isshowninFigure5-10anddescribedinTable5-12.The

oscillatordivider1controlsdividerforOBSCLK,dividingdownfromtheMXI/CLKINclock.ForPLLC1,the

OBSCLKisconnectedtoCLKOUT0pin.OSCDIV1onlyappliestoPLLC1,andshouldnotbeusedon

PLLC2.

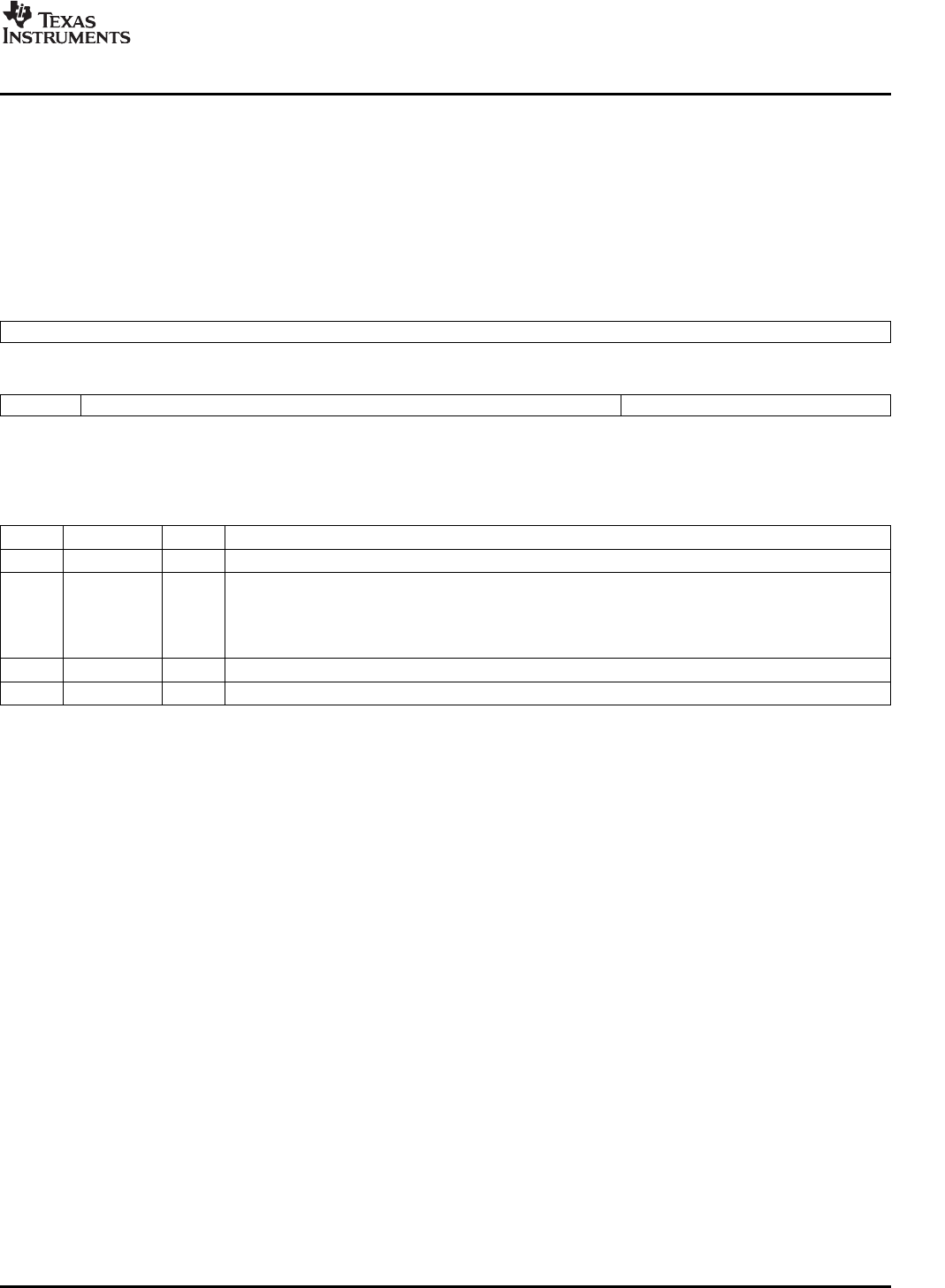

Figure5-10.OscillatorDivider1Register(OSCDIV1)

3116

Reserved

R-0

1514540

OD1ENReservedRATIO

R/W-1R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table5-12.OscillatorDivider1Register(OSCDIV1)FieldDescriptions

BitFieldValueDescription

31-16Reserved0Reserved

15OD1ENOscillatordivider1enable.

0Oscillatordivider1isdisabled.

1Oscillatordivider1isenabled.ForOBSCLKtotoggle,boththeOD1ENbitandtheOBSENbitinthe

clockenablecontrolregister(CKEN)mustbesetto1.

14-5Reserved0Reserved

4-0RATIO0-1FhDividerratio.Dividervalue=RATIO+1.Forexample,RATIO=0meansdivideby1.

SPRU978E–March2008PLLController53

SubmitDocumentationFeedback