www.ti.com

5.4.3PLLControlRegister(PLLCTL)

PLLControllerRegisters

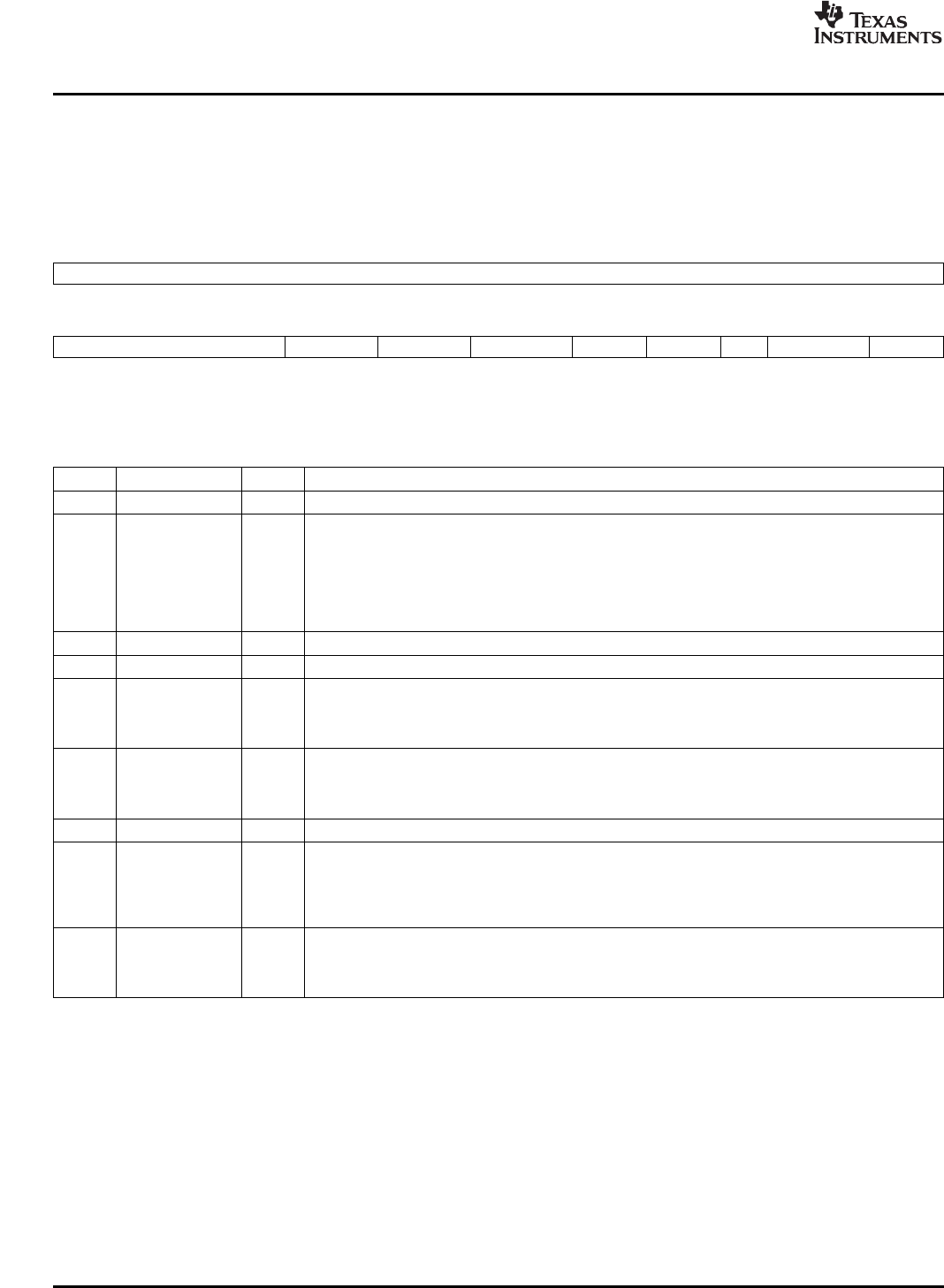

ThePLLcontrolregister(PLLCTL)isshowninFigure5-5anddescribedinTable5-7.

Figure5-5.PLLControlRegister(PLLCTL)

3116

Reserved

R-0

159876543210

ReservedCLKMODEReservedPLLENSRCPLLDISPLLRSTRsvdPLLPWRDNPLLEN

R-0R/W-0R-1hR/W-1R/W-1R/W-0R-0R/W-1R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table5-7.PLLControlRegister(PLLCTL)FieldDescriptions

BitFieldValueDescription

31-9Reserved0Reserved

8CLKMODEReferenceclockselection

0Internaloscillator.IfthedevicereferenceclocksourceisacrystalatMXI/CLKINpin,theinternal

oscillatormustbeselectedastheclocksource.

1CLKINsquarewave.Thismodeappliesifthedevicereferenceclocksourceisasquarewaveat

MXI/CLKINpin.Whenthismodeisselected,thePLLCturnsofftheinternaloscillator'sbiasresistor

tosavepower.

7-6Reserved1Reserved

5PLLENSRC0Thisbitmustbeclearedto0beforePLLENwillhaveanyeffect.

4PLLDISAssertsDISABLEtoPLL.

0PLLdisableisde-asserted.

1PLLdisableisasserted.PLLoutputisdisabledandnottoggling.

3PLLRSTAssertsRESETtoPLLifsupported.

0PLLresetisasserted.Seedevice-specificdatamanualforthePLLresettimerequired.

1PLLresetisnotasserted.

2Reserved0Reserved

1PLLPWRDNPLLpower-down.AfterpoweringupthePLL(PLLPWRDN1to0transition),youmustwaitforthe

PLLtostabilize.Seedevice-specificdatamanualforthePLLstabilizationtime.

0PLLoperational.

1PLLpower-down.

0PLLENPLLmodeenable.

0Bypassmode

1PLLmode,notbypassed

50PLLControllerSPRU978E–March2008

SubmitDocumentationFeedback