48 DS6000 Series: Concepts and Architecture

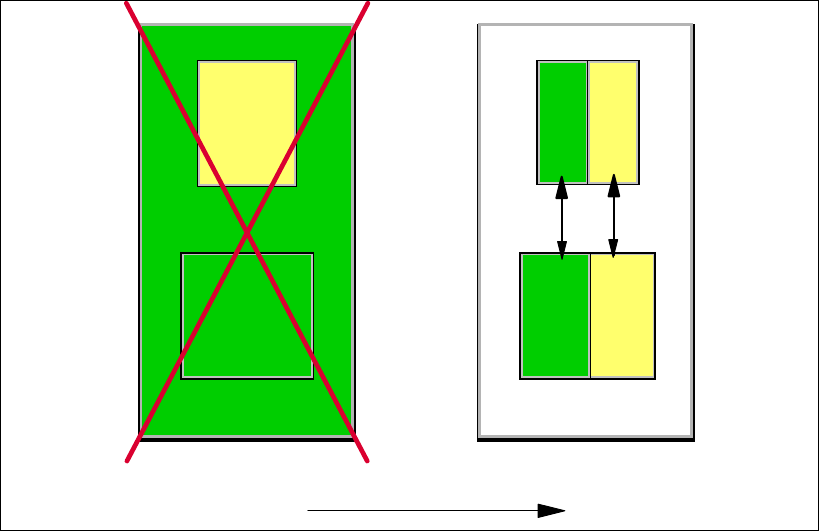

Figure 3-2 Controller failover

This entire process is known as a failover. After failover, controller 1 now owns all the LSSs,

which means all reads and writes will be serviced by controller 1. The NVS inside controller 1

is now used for both odd and even LSSs. The entire failover process should be invisible to the

attached hosts, apart from the possibility of some temporary disk errors.

Failback

When the failed controller has been repaired and restarted, the failback process is activated.

Controller 1 starts using the NVS in controller 0 again, and the ownership of the even LSSs is

transferred back to controller 0. Normal operations with both controllers active then resumes.

Just like the failover process, the failback process is invisible to the attached hosts.

In general, recovery actions on the DS6000 do not impact I/O operation latency by more than

15 seconds. With certain limitations on configurations and advanced functions, this impact to

latency can be limited to 8 seconds. On logical volumes that are not configured with RAID-10

storage, certain RAID-related recoveries may cause latency impacts in excess of 15 seconds.

If you have real-time response requirements in this area, contact IBM to determine the latest

information on how to manage your storage to meet your requirements.

3.1.2 NVS recovery after complete power loss

During normal operation, the DS6800 preserves un-destaged write data using the NVS copy

in the alternate controller. To ensure that these writes are not lost, each controller has a

dedicated battery backup unit (BBU). If this BBU were to fail, the controller would lose this

protection and consequently that controller would remove itself from service. If power is lost to

a single power supply, this does not affect the ability of the other power supply to keep both

BBUs charged, so both controllers would remain online. In other words, there is an affinity

between controllers and BBUs, but not between power supplies and BBUs.

The single purpose of the BBUs is to preserve the NVS area of controller memory in the event

of a complete loss of input power to the DS6800. If both power supplies were to stop receiving

Cache

memory

for even

LSSs

NVS

for odd

LSSs

Failover

NVS

for

even

LSSs

Cache

for

odd

LSSs

Cache

for

even

LSSs

NVS

for

odd

LSSs

Controller 0

Controller 1