88F6281

Hardware Specifications

Doc. No. MV-S104859-U0 Rev. E Copyright © 2008 Marvell

Page 18 Document Classification: Proprietary Information December 2, 2008, Preliminary

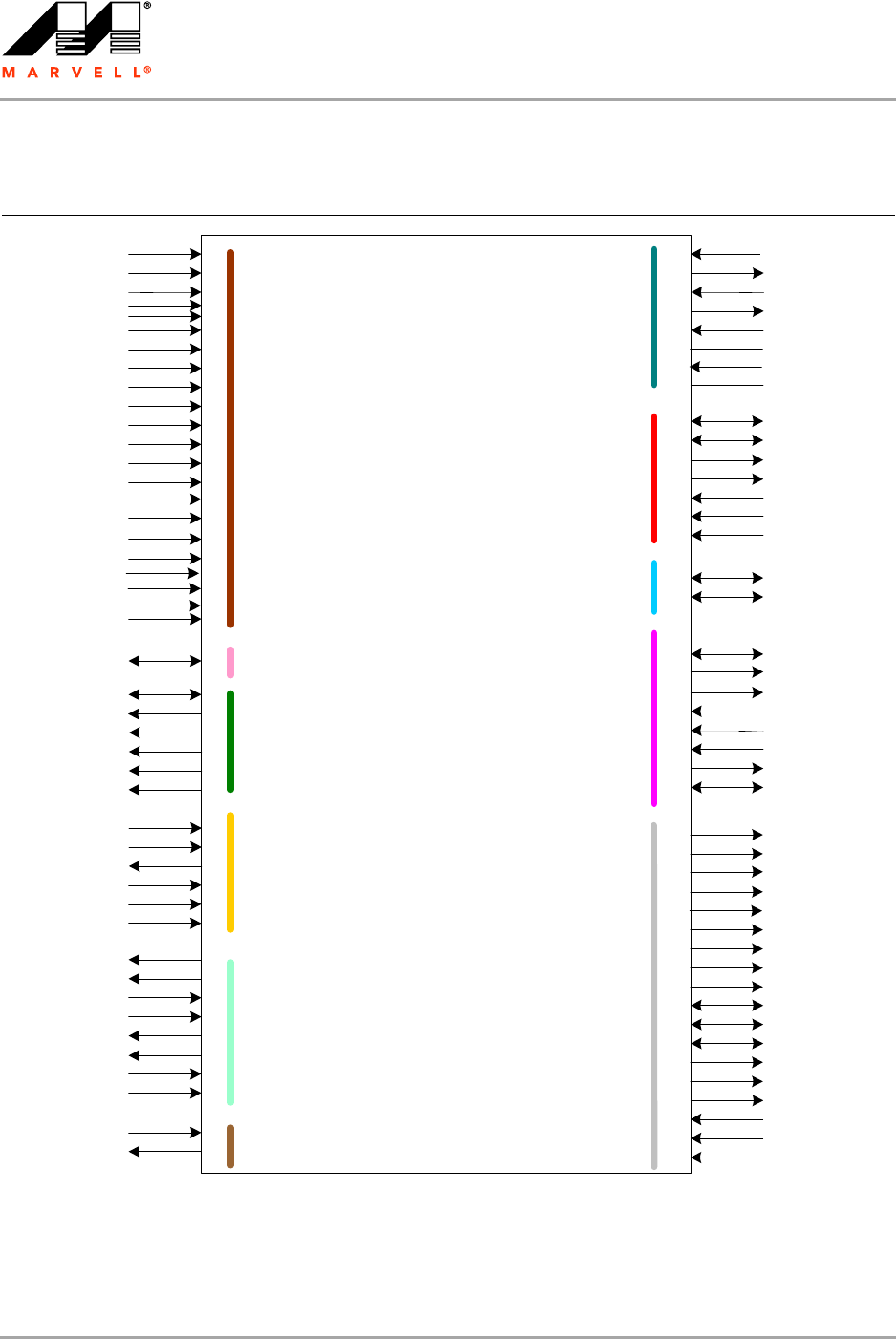

1.1 Pin Logic

Figure 1: 88F6281 Pin Logic Diagram

NOTE: The GE_TXCLKOUT pin is an input only when used as the MII/MMII Transmit Clock.

For details about MPP configuration options see Section 4.1, Multi-Purpose Pins Functional

Summary, on page 51.

Misc.

REF_CLK_XIN

Power

TP

XOUT

SYSRSTn

USB

USB_DM

USB_DP

Gigabit Ethernet

GE_TXCLKOUT

GE_TXCTL

GE_TXD[3:0]

GE_RXD[3:0]

GE_RXCTL

GE_RXCLK

GE_MDC

GE_MDIO

SDRAM

M_CLKOUT

M_CLKOUTn

M_CKE

M_RASn

M_CASn

M_WEn

M_A[14:0]

M_BA[2:0]

M_CSn[3:0]

M_DQ[15:0]

M_DQS[1:0]

M_DQSn[1:0]

M_STARTBURST

M_STARTBURST_IN

M_PCAL

M_NCAL

M_DM[1:0]

M_ODT[1:0]

RTC

RTC_XIN

RTC_XOUT

SATA0/1

SATA0_T_P

SATA0_R_P

SATA0_R_N

SATA0_T_N

SATA1_T_P

SATA1_T_N

SATA1_R_P

SATA1_R_N

JTAG

JT_CLK

JT_TDI

JT_TDO

JT_TMS_CORE

JT_RSTn

JT_TMS_CPU

NAND

Flash

NF_CLE

NF_ALE

NF_CEn

NF_REn

NF_WEn

NF_IO[7:0]

MPP

MPP[49:0]

RESERVED

NC

ISET

MRn

CPU_PLL_AVDD

CORE_PLL_AVDD

XTAL_AVDD

SATA0_AVDD

SATA1_AVDD

CPU_PLL_AVSS

CORE_PLL_AVSS

XTAL_AVSS

VDD_M

VSS

VDDO

VDD_CPU

VDD

VDD_GE_A

PEX_AVDD

RTC_AVDD

USB_AVDD

SSCG_AVDD

SSCG_AVSS

RTC_AVSS

VHV

PCI Express

PEX_TX_P

PEX_TX_N

PEX_RX_P

PEX_RX_N

PEX_ISET

PEX_CLK_N

PEX_CLK_P

VDD_GE_B