JTAG Interface

TAP Controller

Copyright © 2008 Marvell Doc. No. MV-S104859-U0 Rev. E

December 2, 2008, Preliminary Document Classification: Proprietary Information Page 73

7 JTAG Interface

To enable board testing, the device supports a test mode operation through its JTAG boundary scan

interface.

The JTAG interface is IEEE 1149.1 standard compliant. It supports mandatory and optional

boundary scan instructions.

7.1 TAP Controller

The Test Access Port (TAP) is constructed with a 5-pin interface and a 16-state Finite State Machine

(FSM), as defined by IEEE JTAG standard 1149.1.

To place the device in a functional mode, reset the JTAG state machine to disable the JTAG

interface.

According to the IEEE 1149.1 standard, the JTAG state machine is not reset when the 88F6281

SYSRSTn is asserted. The JTAG state machine can only be reset by one of the following methods:

Asserting JT_RSTn.

Setting JT_TMS_CORE for at least five JT_CLK cycles.

To place the device in one of the boundary scan test mode, the JTAG state machine must be moved

to its control states. JT_TMS_CORE and JT_TDI inputs control the state transitions of the JTAG

state machine, as specified in the IEEE 1149.1 standard. The JTAG state machine will shift

instructions into the Instruction register while in SHIFT-IR state and shift data into and from the

various data registers when in SHIFT-DR state.

7.2 Instruction Register

The Instruction register (IR) is a 4-bit, two-stage register. It contains the command that is shifted in

when the TAP FSM is in the Shift-IR state. When the TAP FSM is in the Capture-IR state, the IR

outputs all four bits in parallel.

Table 33 lists the instructions supported by the device.

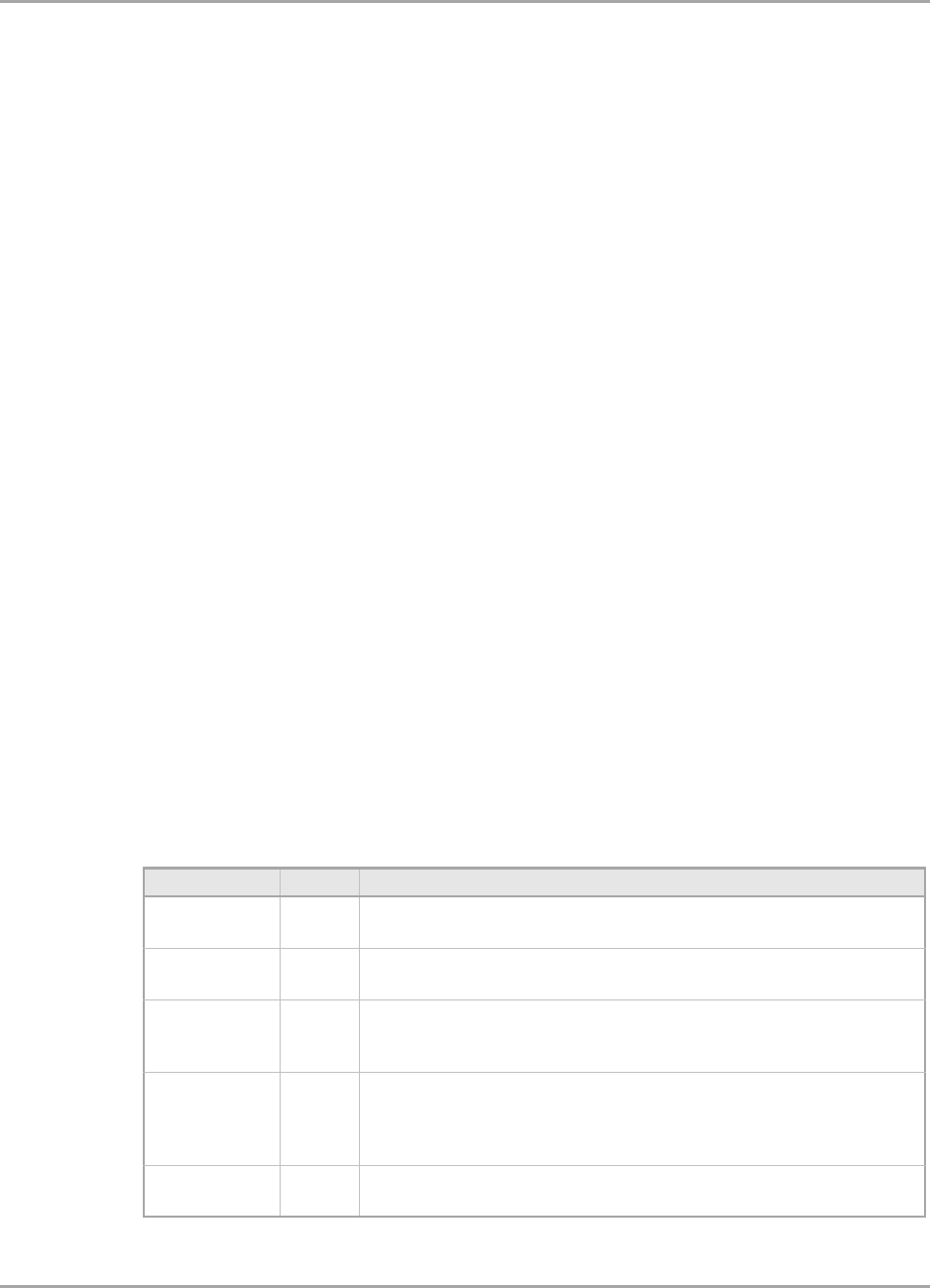

Table 33: Supported JTAG Instructions

Instruction Code Description

HIGHZ 0011 Select the single bit Bypass register between TDI and TDO.

Sets the device output pins to high-impedance state.

IDCODE 0010 Selects the Identification register between TDI and TDO. This 32-bit

register is used to identify the device.

EXTEST 0000 Selects the Boundary Scan register between TDI and TDO. Outputs the

boundary scan register cells to drive the output pins of the device. Inputs

the boundary scan register cell to sample the input pin of the device.

SAMPLE/PRE

LOAD

0001 Selects the Boundary Scan register between TDI and TDO. Samples

input pins of the device to input boundary scan register cells.

Preloads the output boundary scan register cells with the Boundary Scan

register value.

BYPASS 1111 Selects the single bit Bypass register between TDI and TDO. This allows

for rapid data movement through an untested device.