88F6281

Hardware Specifications

Doc. No. MV-S104859-U0 Rev. E Copyright © 2008 Marvell

Page 86 Document Classification: Proprietary Information December 2, 2008, Preliminary

8.6 AC Electrical Specifications

See Section 8.7, Differential Interface Electrical Characteristics, on page 118 for differential interface

specifications.

8.6.1 Reference Clock AC Timing Specifications

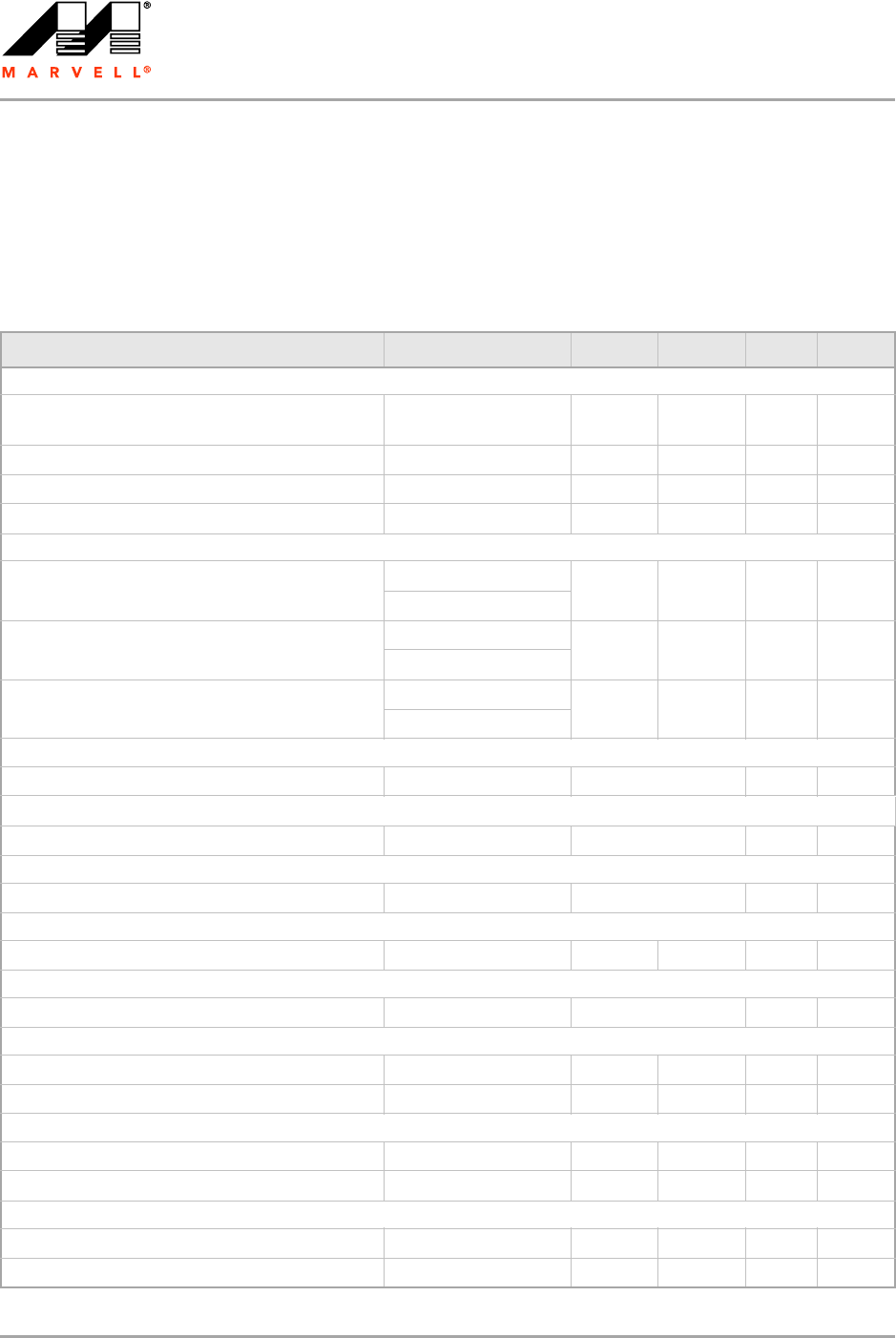

Table 45: Reference Clock AC Timing Specifications

Description Symbol Min Max Units Notes

CPU and Core Reference Clock

Frequency F

REF_CLK_XIN

25 -

50 ppm

25 +

50 ppm

MHz

Clock duty cycle DC

REF_CLK_XIN

40 60 %

Slew rate SR

REF_CLK_XIN

0.7 V/ns 1

Pk-Pk jitter JR

REF_CLK_XIN

200 ps

Ethernet Reference Clock

Frequency in MII/MMII-MAC mode F

GE_TXCLK_OUT

2.5 -

100 ppm

50 +

100 ppm

MHz 7

F

GE_RXCLK

MII/MMII-MAC mode clock duty cycle DC

GE_TXCLK_OUT

35 65 % 7

DC

GE_RXCLK

Slew rate SR

GE_TXCLK_OUT

0.7 V/ns 1, 7

SR

GE_RXCLK

Audio External Reference Clock

Audio external reference clock F

AU_EXTCLK

256 X F

s

kHz 3

S/PDIF Recovered Master Clock

S/PDIF recovered master clock F

AU_SPDFRMCLK

256 X F

s

kHz 3

I

2

S Reference Clock

I

2

S clock F

I2S_BCLK

64 X F

s

kHz 3

SPI Output Clock

SPI output clock F

SPI_SCK

TCLK/30 TCLK/4 MHz 2

RTC Reference Clock

RTC_XIN crystal frequency F

RTC_XIN

32.768 kHz 4

Transport Stream (TS) Output Mode Reference Clock

TS output clock in parallel mode F

TS0_CLK,

F

TS1_CLK

9.61 12.5 MHz 5

TS output clock in serial mode F

TS0_CLK,

F

TS1_CLK

9.61 83 MHz 5

Transport Stream Input Mode Reference Clock

TS input clock in parallel mode F

TS0_CLK,

F

TS1_CLK

13.5 MHz

TS input clock in serial mode F

TS0_CLK,

F

TS1_CLK

83 MHz

Transport Stream External Reference Clock

TS external clock in parallel mode F

EXT_CLK

9.61 12.5 MHz 5

TS external clock in serial mode F

EXT_CLK

9.61 83 MHz 5