88F6281

Hardware Specifications

Doc. No. MV-S104859-U0 Rev. E Copyright © 2008 Marvell

Page 44 Document Classification: Proprietary Information December 2, 2008, Preliminary

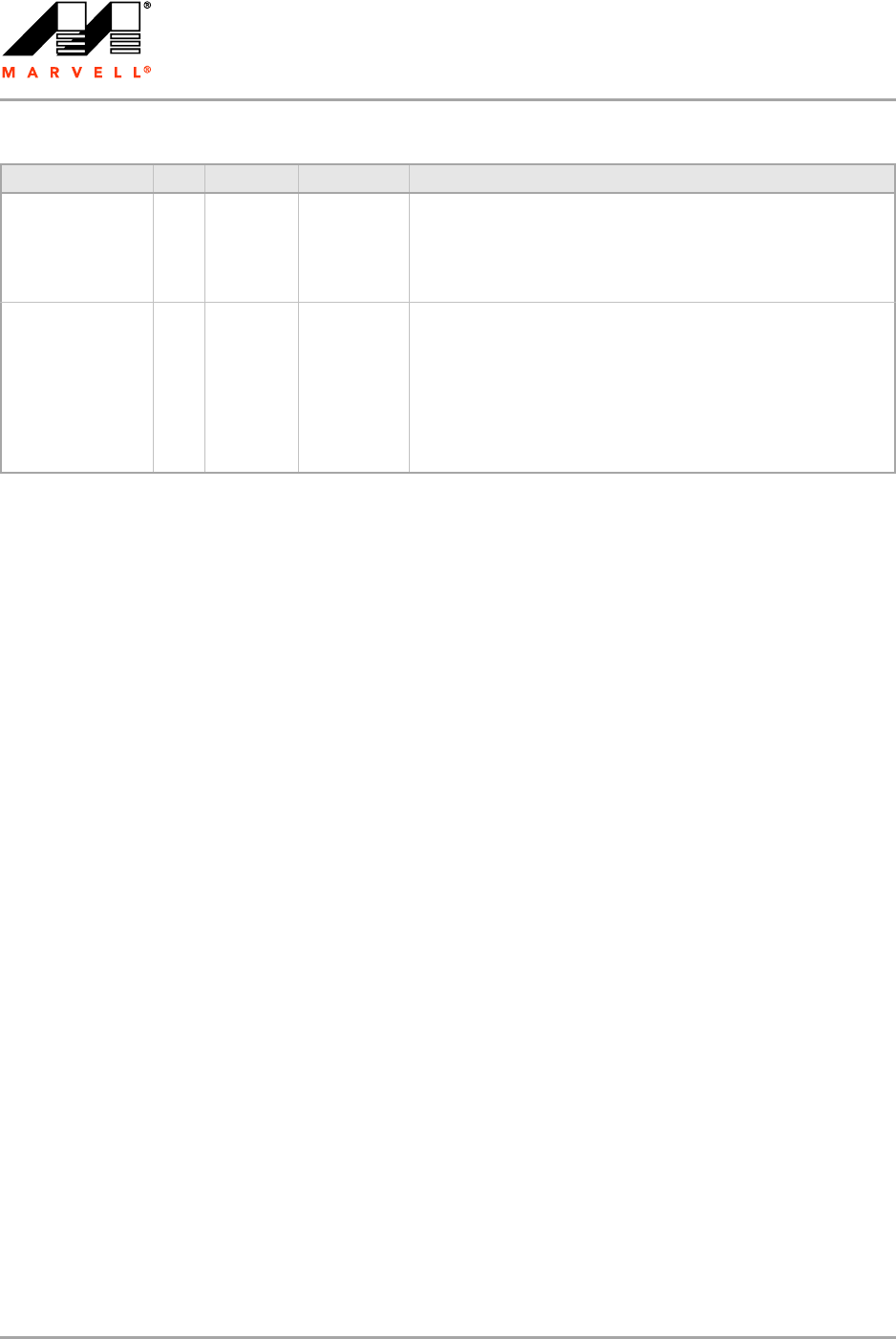

TDM_SPI_MOSI O CMOS VDDO/

VDD_GE_B

Serial SPI data from the host to the codec for register access.

When TDM_SPI_CS is asserted low, the data is driven from the

host on the negative edge of TDM_SPI_SCK. It is always driven

for eight TDM_SPI_SCK cycles at a time.

In a byte, the data can be driven MSB or LSB first.

TDM_SPI_MISO I CMOS VDDO/

VDD_GE_B

Serial SPI read data from the CODEC to the host for register

access.

When TDM_SPI_CS is asserted low, this data is driven from

CODEC on negative edge of TDM_SPI_SCK. It is always driven

for eight TDM_SPI_SCK cycles at a time. The CODEC drives

data on this line only for a read operation, when it gets command

and address in previous bytes from the host on TDM_SPI_MOSI

In a byte, the data can be driven MSB or LSB first.

Table 20: Time Division Multiplexing (TDM) Interface Signal Assignment (Continued)

Pin Name

I/O

Pin Type Power Rail

Description