88F6281

Hardware Specifications

Doc. No. MV-S104859-U0 Rev. E Copyright © 2008 Marvell

Page 60 Document Classification: Proprietary Information December 2, 2008, Preliminary

5 Clocking

Table 29 lists the clocks in the 88F6281.

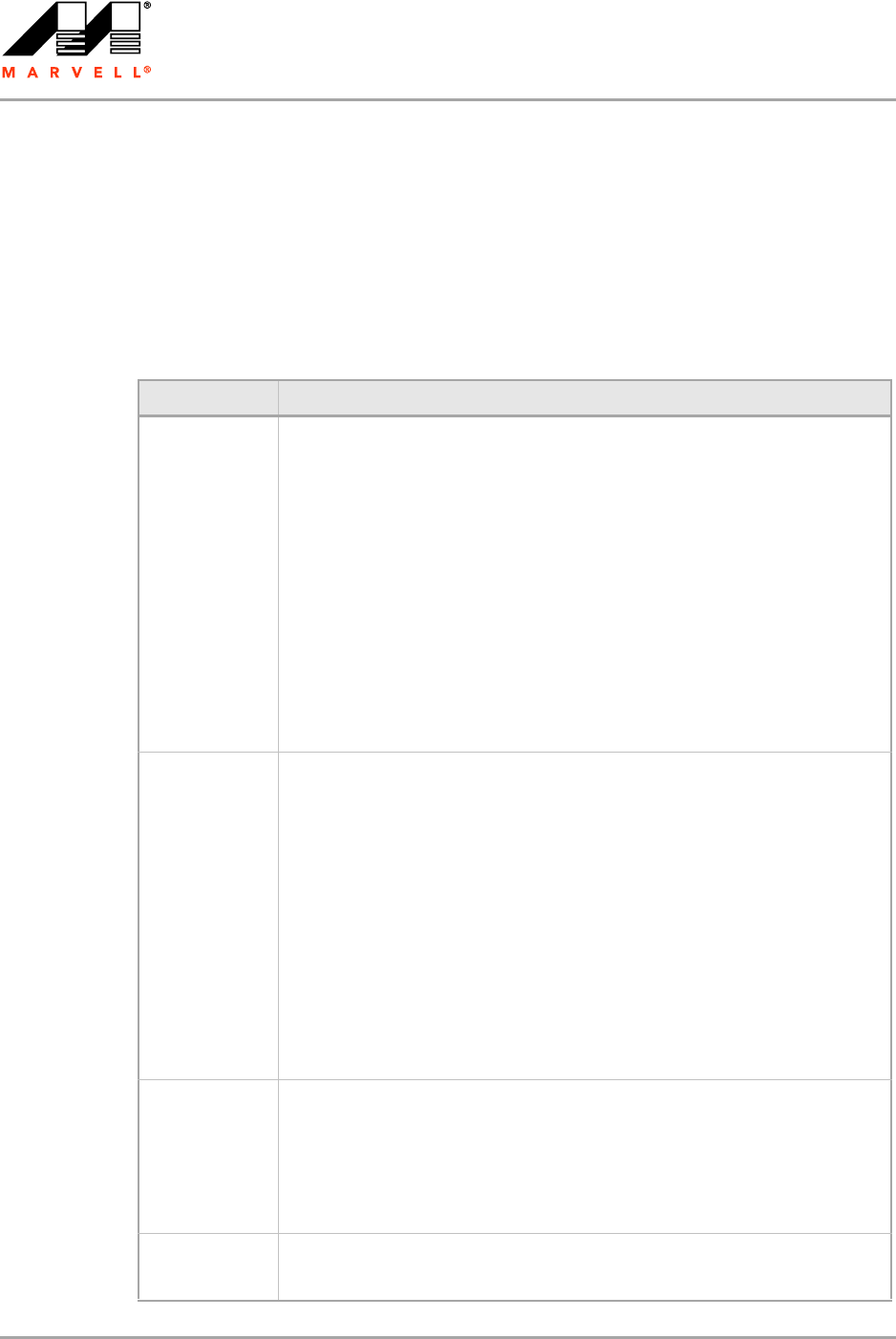

Table 29: 88F6281Clocks

Clock Type Description

CPU PLL

• Reference clock:

REF_CLK_XIN (25 MHz)

• Derivative clocks:

- CPU clock

- L2 cache clock

- DDR Clock (the Mbus-L uses the DDR clock.)

NOTE: See Table 32, Reset Configuration, on page 67 for CPU, L2 cache and

DDR frequency configuration.

L2 cache clock frequency must be equal or higher then DDR clock

frequency.

If the SSCG enable bit in the Sampled at Reset register is set, then the

SSCG circuit is applied for the CPU PLL reference clock (refer to the

Sampled at Reset register in the 88F6180, 88F6190, 88F6192, and

88F6281 Functional Specifications).

Core PLL

• Reference clock:

REF_CLK_XIN (25 MHz)

• Derivative clocks:

- TCLK (core clock, 200 MHz)

- SDIO Clock (100 MHz)

- Gigabit Ethernet Clock (125 MHz)

- TS unit Clock(100/91/83/77MHz)

- SPI clock (TCLK/30–TCLK/4 MHz)

- SMI clock (TCLK/128 MHz)

- TWSI clock (up to TCLK/1600)

NOTE: See Table 32, Reset Configuration, on page 67 for TCLK frequency

configuration.

NOTE: See the TS Interface Configuration register in the 88F6180, 88F6190,

88F6192, and 88F6281 Functional Specifications for TS clock frequency

configuration.

PEX PHY

There are two options for the reference clock configuration, depending on the PCI

Express clock 100 MHz differential clock:

• The device uses an external source for PCI Express clock. The PEX_CLK_P

pin is an input.

• The device uses an internal generated clock for PCI Express clock. The

PEX_CLK_P pin is an output, driving out the PCI Express differential clock.

USB PHY PLL

• Reference clock:

REF_CLK_XIN (25 MHz)