88F6281

Hardware Specifications

Doc. No. MV-S104859-U0 Rev. E Copyright © 2008 Marvell

Page 46 Document Classification: Proprietary Information December 2, 2008, Preliminary

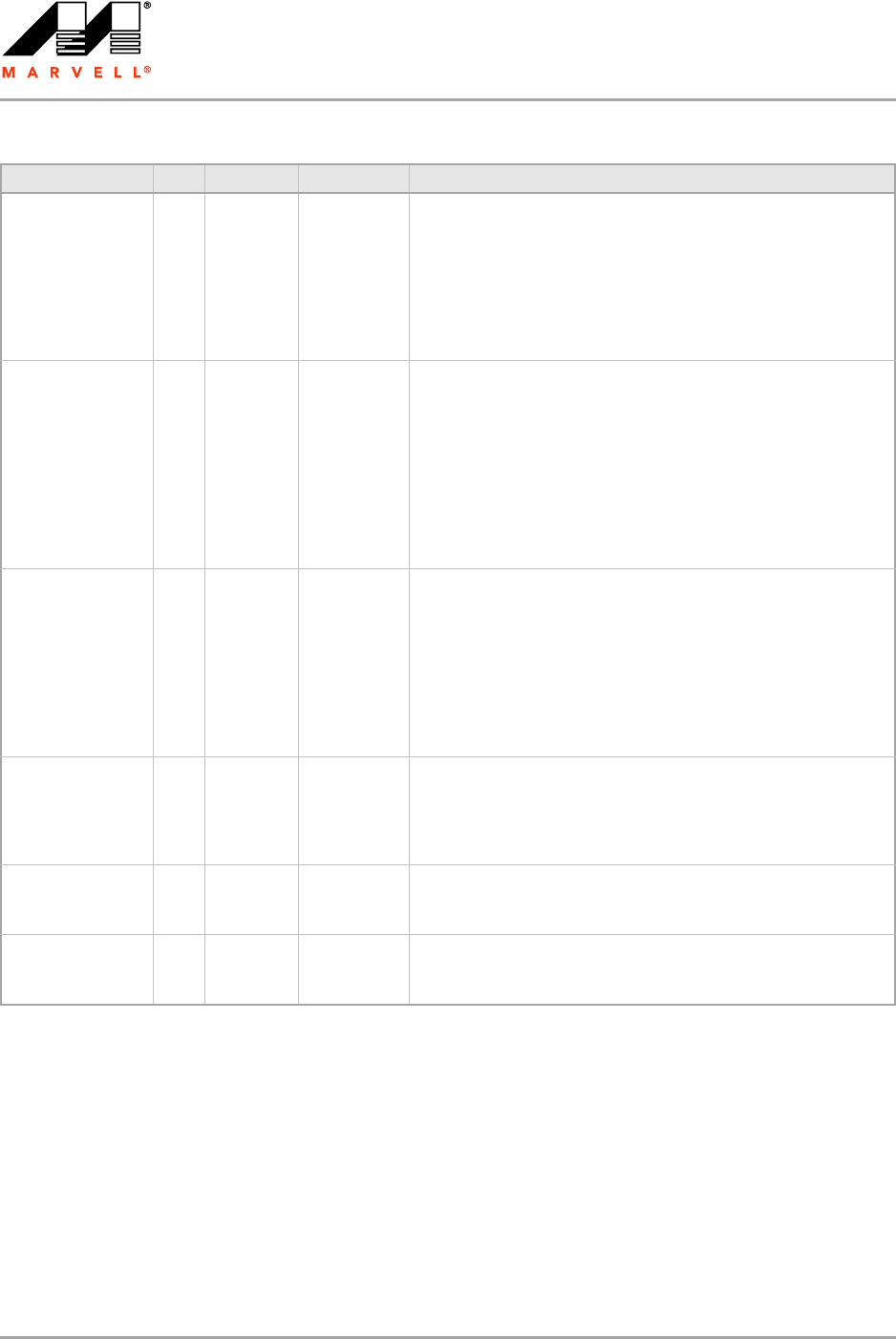

TSMP[7] I/O CMOS VDDO/

VDD_GE_B

• Parallel Mode:

TS0_DATA[2]: Port0 TS Data bit 2

• Serial Mode:

TS1_SYNC: Port1 Sync/Frame Start Indicator or Packet

Clock.

The TS1_SYNC pulse may be active for the entire byte or

only for the first bit. The polarity is programmable to be either

active high or active low

TSMP[8] I/O CMOS VDDO/

VDD_GE_B

• Parallel Mode:

TS0_DATA[3]: Port0 TS Data bit 3

• Serial Mode:

TS1_VAL: Port1Valid Data Indicator

When this signal is used and is valid, it indicates that valid

data is present on TS1_DATA[0].

TS1_VAL is active during the TS frame packet data and

inactive when there is no TS synchronization.

In output mode, the polarity of TS1_VAL is programmable to

be either active high or active low.

TSMP[9] I/O CMOS VDDO/

VDD_GE_B

• Parallel Mode:

TS0_DATA[4]: Port0 TS Data bit 4

• Serial Mode:

TS1_ERR: Port1 Uncorrectable Packet Error

When this signal is used, an error indicates that the packet

contains an uncorrectable error, and, therefore, should not

be used.

In output mode the TS1_ERR is active during the entire TS

frame.

TSMP[10] I/O CMOS VDDO/

VDD_GE_B

• Parallel Mode:

TS0_DATA[5]: Port0 TS Data bit 5

• Serial Mode:

TS1_DATA[0]: Port1 TS Data bit 0, used as data input or

output.

TSMP[11] I/O CMOS VDDO/

VDD_GE_B

TS0_DATA[6]

Port0 TS Data bit 6

This pin is only valid in Parallel mode.

TSMP[12] I/O CMOS VDDO/

VDD_GE_B

TS0_DATA[7]

Port0 TS Data bit 7

This pin is only valid in Parallel mode.

Table 21: Transport Stream (TS) Interface Signal Assignment (Continued)

Pin Name

I/O

Pin Type Power Rail

Description