www.ti.com

2.3SignalDescriptions

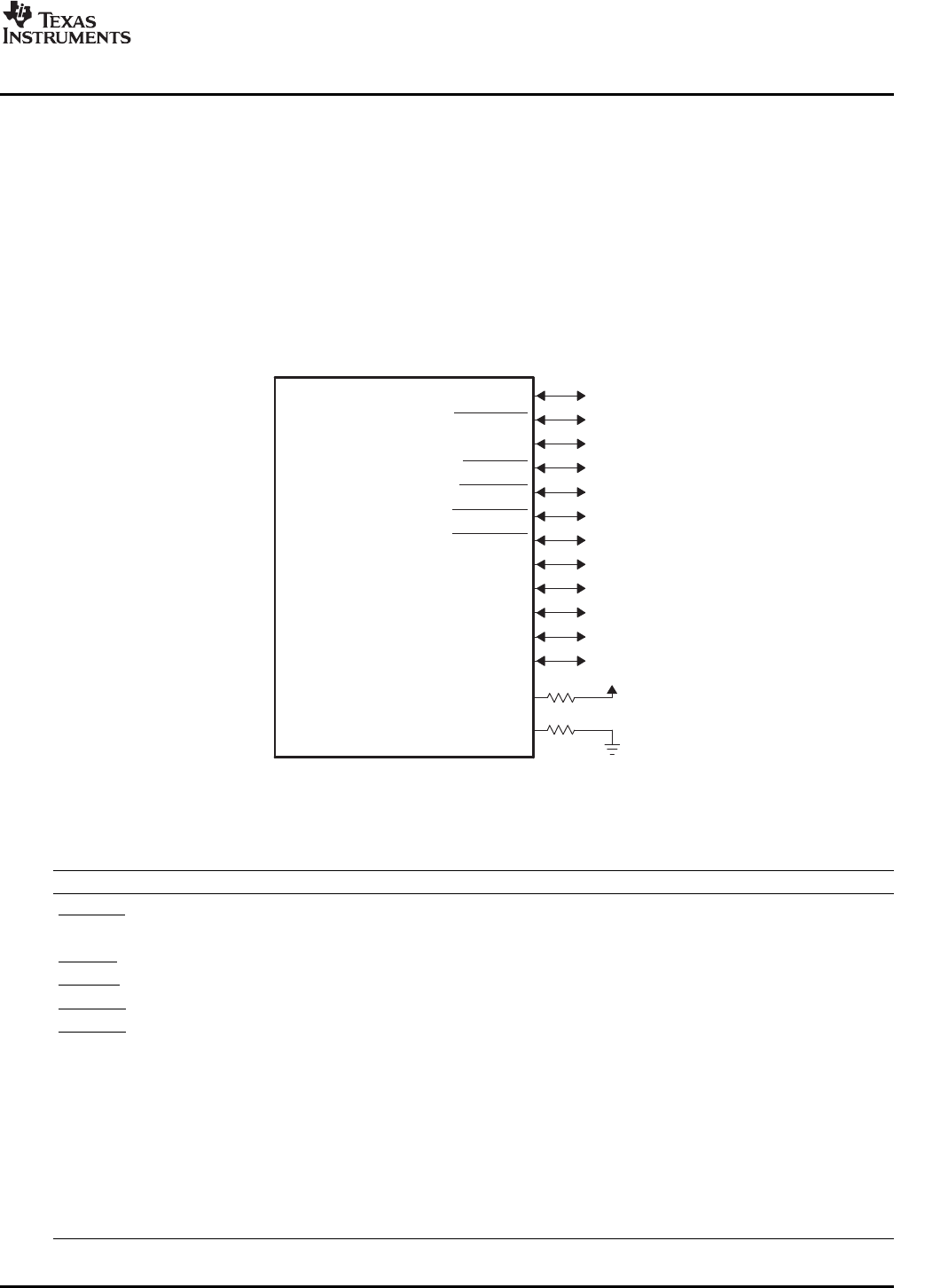

DDR_D[31:0]

DDR2

memory

controller

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_DQM[3:0]

DDR_CAS

DDR_BA[2:0]

DDR_DQS[3:0]

DDR_A[12:0]

DDR_ZN

DDR_ZP

200 Ω

200 Ω

PeripheralArchitecture

TheDDR2memorycontrollersignalsareshowninFigure3anddescribedinTable2.Thefollowing

featuresareincluded:

•Themaximumdatabusis32-bitswide.

•Theaddressbusis13-bitswidewithanadditional3bankaddresspins.

•Twodifferentialoutputclocksdrivenbyinternalclocksources.

•Commandsignals:Rowandcolumnaddressstrobe,writeenablestrobe,datastrobe,anddatamask.

•Onechipselectsignalandoneclockenablesignal.

Figure3.DDR2MemoryControllerSignals

Table2.DDR2MemoryControllerSignalDescriptions

PinTypeDescription

DDR_CLK,O/ZClock:Differentialclockoutputs.

DDR_CLK

DDR_CKEO/ZClockenable:Activehigh.

DDR_CSO/ZChipselect:Activelow.

DDR_WEO/ZWriteenablestrobe:Activelow,commandoutput.

DDR_RASO/ZRowaddressstrobe:Activelow,commandoutput.

DDR_CASO/ZColumnaddressstrobe:Activelow,commandoutput.

DDR_DQM[3:0]O/ZDatamask:Outputmasksignalforwritedata.

DDR_DQS[3:0]I/O/ZDatastrobe:Activehigh,bi-directionalsignals.Outputwithwritedata,inputwithreaddata.

DDR_BA[2:0]O/ZBankaddress:Output,definingwhichbankagivencommandisapplied.

DDR_A[12:0]O/ZAddress:Addressbus.

DDR_D[31:0]I/O/ZData:Bi-directionaldatabus.Inputforreaddata,outputforwritedata.

DDR_ZN,OOutputimpedancecontrol:RequiredtosettheDDR2outputimpedance.Connectedbywayof

DDR_ZPa200-ohmresistortopowerandground(seeFigure3).Theresistorshouldbechosentobe

4timesthedesiredimpedanceoftheoutputbuffer.Bychangingthesizeoftheresistor,the

DDR2outputscanbetunedtomatchtheboardload,ifnecessary.

SPRU986B–November2007DDR2MemoryController11

SubmitDocumentationFeedback