www.ti.com

4.3SDRAMRefreshControlRegister(SDRCR)

DDR2MemoryControllerRegisters

TheSDRAMrefreshcontrolregister(SDRCR)isusedtoconfiguretheDDR2memorycontrollerto:

•EnterandExittheself-refreshstate.

•EnableanddisableMCLK,stoppingwhenintheself-refreshstate.

•MeettherefreshrequirementoftheattachedDDR2devicebyprogrammingtherateatwhichthe

DDR2memorycontrollerissuesautorefreshcommands.

TheSDRCRisshowninFigure21anddescribedinTable27.

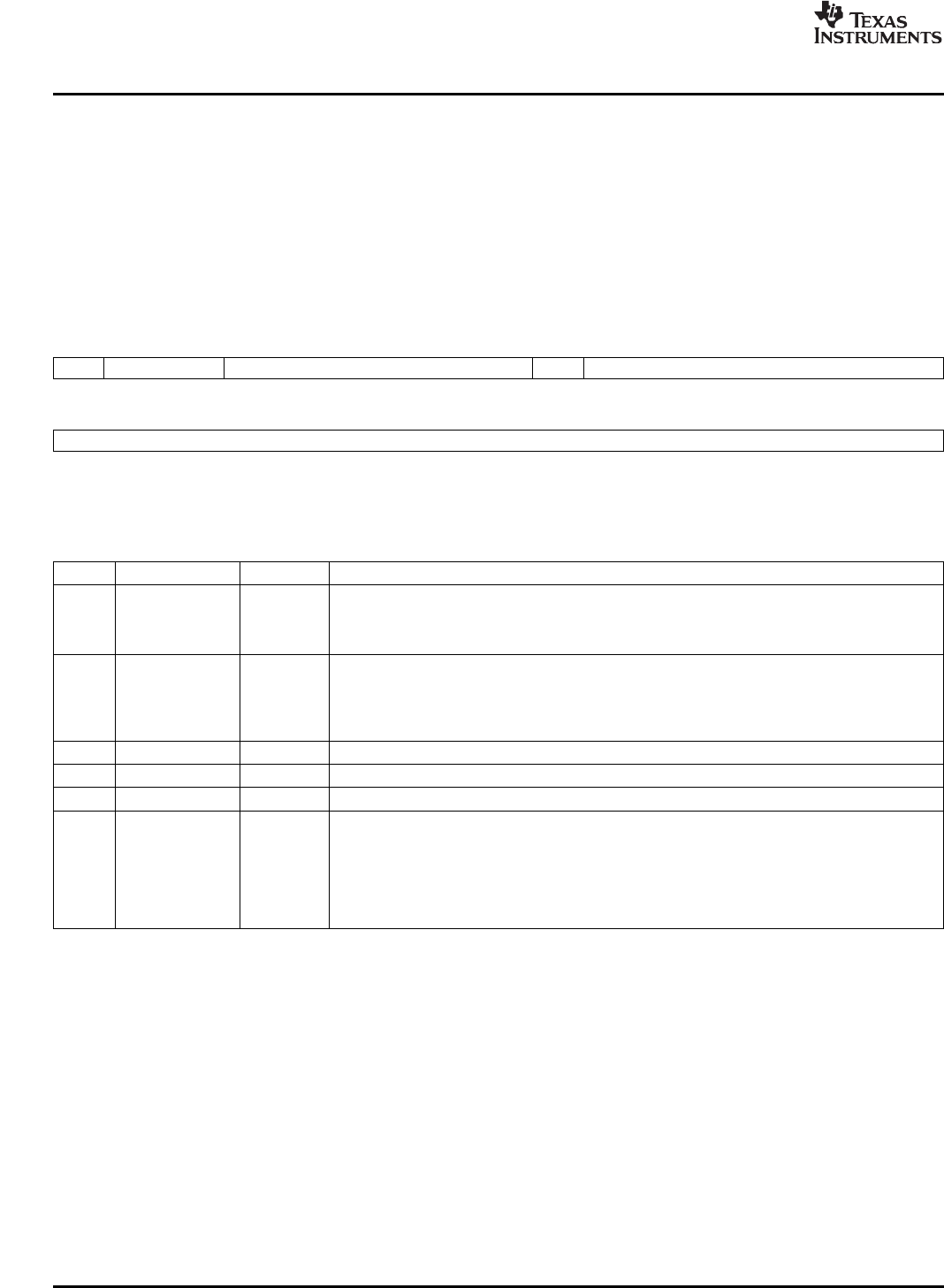

Figure21.SDRAMRefreshControlRegister(SDRCR)

31302924232216

SRMCLKSTOPENReservedRsvdReserved

R/W-0R/W-0R-0R/W-0R-0

150

RR

R/W-884h

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table27.SDRAMRefreshControlRegister(SDRCR)FieldDescriptions

BitFieldValueDescription

31SRSelfrefresh.

0DDR2memorycontrollerexitstheself-refreshmode.

1DDR2memorycontrollerenterstheself-refreshmode.

30MCLKSTOPENMCLKstopenable.

0DisablesMCLKstopping,MCLKmaynotbestopped.

1EnablesMCLKstopping,MCLKmaybestopped.TheSRbitmustbesetto1beforesettingthe

MCLKSTOPENbitto1.

29-24Reserved0Reserved

23Reserved0Reserved.Alwayswrite0tothisbit.

22-16Reserved0Reserved

15-0RR0-FFFFhRefreshrate.DefinestherateatwhichtheattachedDDR2deviceswillberefreshed.Thevalue

ofthisfieldmaybecalculatedwiththefollowingequation:

RR=DDR2clockfrequency(inMHZ)×DDR2refreshrate(inµs)

whereDDR2refreshrateisderivedfromtheDDR2datasheet.Writingavalue<0100htothis

fieldcausesittobeloadedwiththevalue2×T_RFCfromtheSDRAMtimingregister

(SDTIMR).

44DDR2MemoryControllerSPRU986B–November2007

SubmitDocumentationFeedback