www.ti.com

0 1 2 3 MBank 0

Row 0

Row 1

Row 2

Row N

C

o

l l

C

o

l

C

o

l

C

o

Row 0

Row N

Row 1

Row 2

CC

Bank 1

l l

0 21

oo

C C

l l

3 M

o o

Row 0

Row N

Row 1

Row 2

CC

Bank 2

l l

0 21

oo

llll

Row N

Row 2

Row 0

Row 1

Bank P 0 1 2 3 M

C C

l l

3 M

o o

o

C

o

C

o

C

o

C

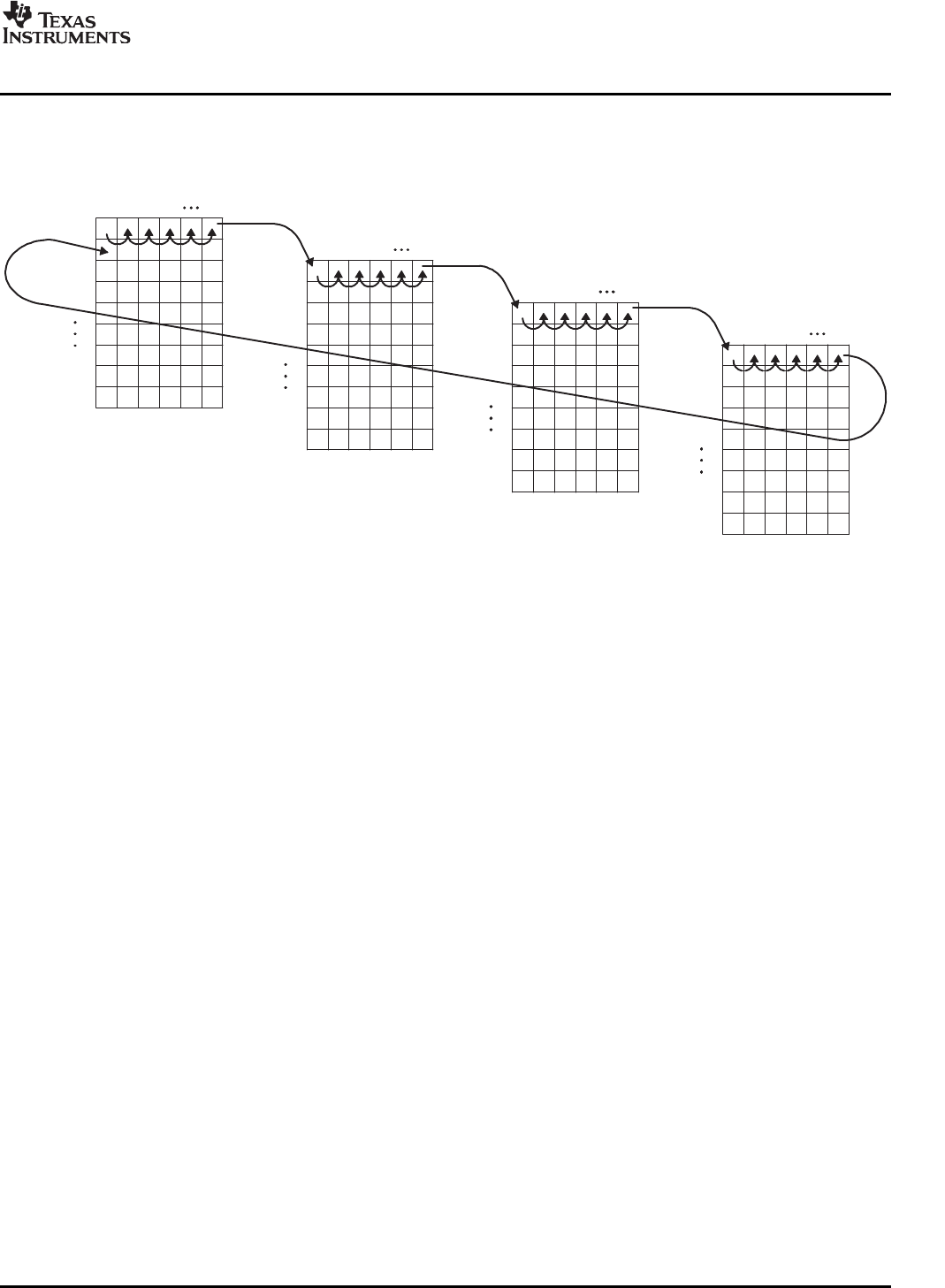

PeripheralArchitecture

Figure13.DDR2SDRAMColumn,Row,andBankAccess

NOTE:Misnumberofcolumns(asdeterminedbyPAGESIZE)minus1,Pisnumberofbanks(asdeterminedby

IBANK)minus1,andNisnumberofrows(asdeterminedbybothPAGESIZEandIBANK)minus1.

SPRU986B–November2007DDR2MemoryController25

SubmitDocumentationFeedback