www.ti.com

2.11ResetConsiderations

DDR2

memory

controller

registers

Hard

Reset from

PLLC1

State

machine

VRST

VCTL_RST

DDR

PSC

PeripheralArchitecture

Onceinself-refreshmode,theDDR2memorycontrollerinputclocks(VCLKandX2_CLK)maybegated

offorchangedinfrequency.Stableclocksmustbepresentbeforeexitingself-refreshmode.See

Section2.16formoreinformationdescribingtheproperproceduretofollowwhenshuttingdownDDR2

memorycontrollerinputclocks.

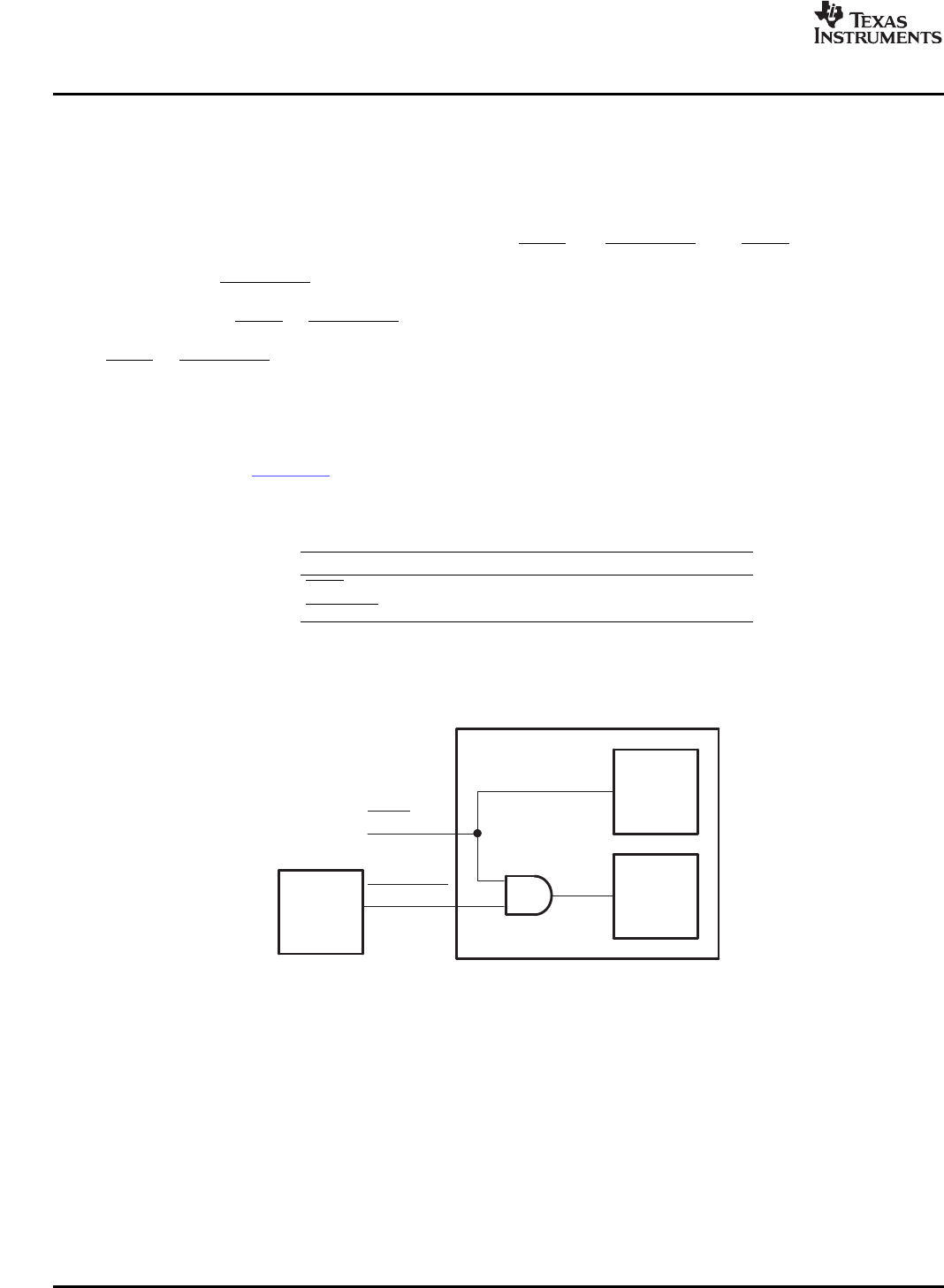

TheDDR2memorycontrollerhastworesetsignals,VRSTandVCTL_RST.TheVRSTisamodule-level

resetthatresetsboththestatemachineaswellastheDDR2memorycontrollermemory-mapped

registers.TheVCTL_RSTresetsthestatemachineonly.IftheDDR2memorycontrollerisreset

independentlyofotherperipherals,theuser'ssoftwareshouldnotperformmemory,aswellasregister

accesses,whileVRSTorVCTL_RSTareasserted.Ifmemoryorregisteraccessesareperformedwhile

theDDR2memorycontrollerisintheresetstate,othermastersmayhang.Followingtherisingedgeof

VRSTorVCTL_RST,theDDR2memorycontrollerimmediatelybeginsitsinitializationsequence.

CommandanddatastoredintheDDR2memorycontrollerFIFOsarelost.Table13describesthedifferent

methodsforassertingeachresetsignal.ThePowerandSleepController(PSC)actsasamaster

controllerforpowermanagementforalloftheperipheralsonthedevice.Fordetailedinformationon

powermanagementproceduresusingthePSC,seetheTMS320DM643xDMPDSPSubsystem

ReferenceGuide(SPRU978).Figure15showstheDDR2memorycontrollerresetdiagram.

Table13.ResetSources

ResetSignalResetSource

VRSTHardware/devicereset

VCTL_RSTPowerandsleepcontroller

Figure15.DDR2MemoryControllerResetBlockDiagram

DDR2MemoryController 30SPRU986B–November2007

SubmitDocumentationFeedback