www.ti.com

4.5SDRAMTimingRegister2(SDTIMR2)

DDR2MemoryControllerRegisters

LiketheSDRAMtimingregister(SDTIMR),theSDRAMtimingregister2(SDTIMR2)alsoconfiguresthe

DDR2memorycontrollertomeettheACtimingspecificationoftheDDR2memory.TheSDTIMR2register

isprogrammableonlywhentheTIMUNLOCKbitissetto1intheSDBCR.SeetheDDR2datasheetfor

informationontheappropriatevaluestoprogrameachfield.SDTIMR2isshowninFigure23and

describedinTable29.

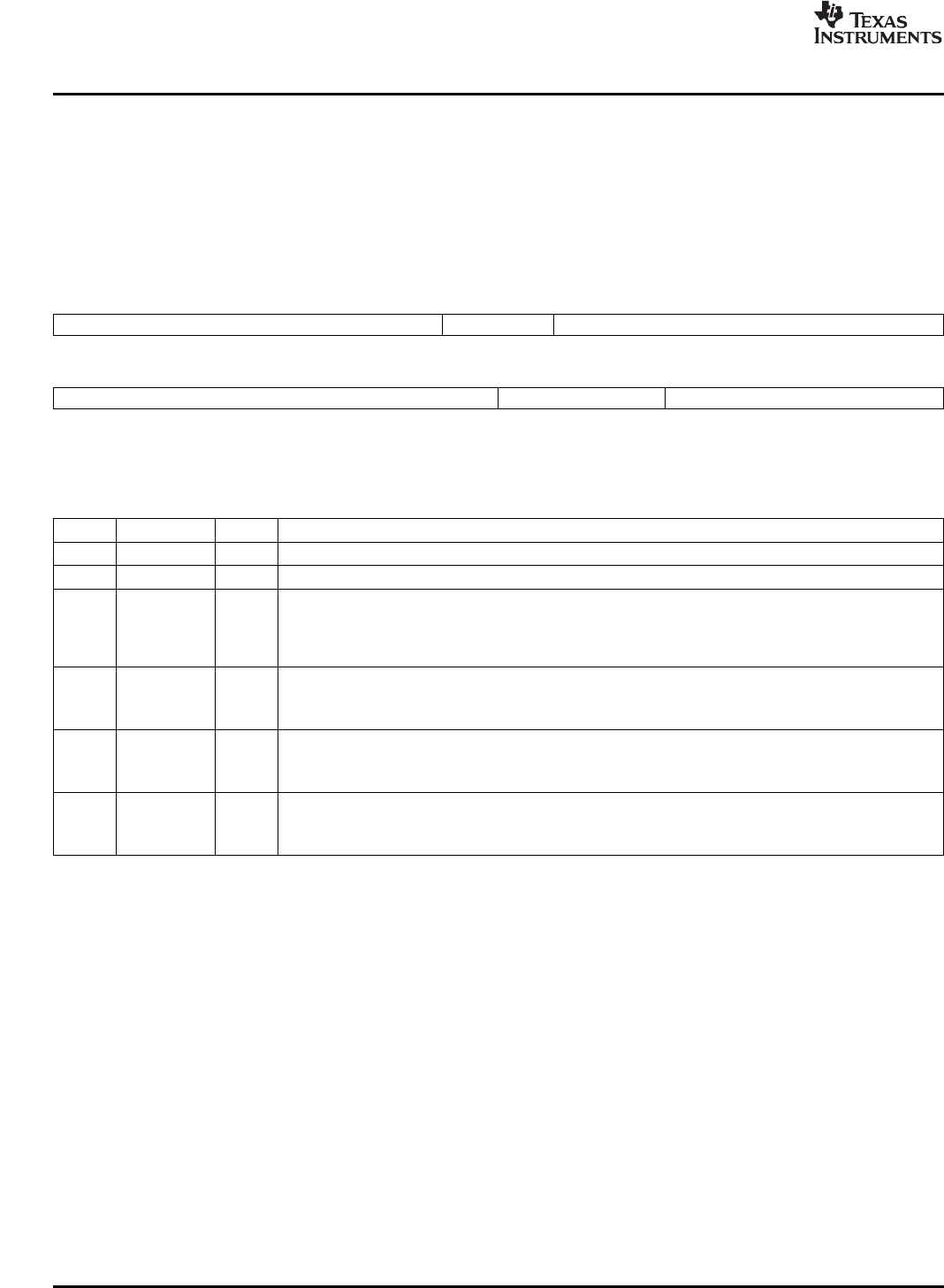

Figure23.SDRAMTimingRegister2(SDTIMR2)

312524232216

ReservedReservedT_XSNR

R-0R/W-xR/W-1Dh

1587540

T_XSRDT_RTPT_CKE

R/W-F1hR/W-2hR/W-5h

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset;-x=valueisindeterminateafterreset

Table29.SDRAMTimingRegister2(SDTIMR2)FieldDescriptions

BitFieldValueDescription

31-25Reserved0Reserved

24-23ReservedxReserved.Resetvalueisindeterminate.

22-16T_XSNR0-7FhSpecifiestheminimumnumberofDDR_CLKcyclesfromaself-refreshexittoanyothercommand

exceptareadcommand,minus1.Correspondstothet

xsnr

ACtimingparameterintheDDR2data

sheet.Calculateby:

T_XSNR=(t

xsnr

/DDR_CLKperiod)-1

15-8T_XSRD0-FFhSpecifiestheminimumnumberofDDR_CLKcyclesfromaself-refreshexittoareadcommand,

minus1.Correspondstothet

xsrd

ACtimingparameterintheDDR2datasheet.Calculateby:

T_XSRD=t

xsrd

-1

7-5T_RTP0-7hSpecifiestheminimumnumberofDDR_CLKcyclesfromalastreadcommandtoaprecharge

command,minus1.Correspondstothet

rtp

ACtimingparameterintheDDR2datasheet.Calculateby:

T_RTP=(t

rtp

/DDR_CLKperiod)-1

4-0T_CKE0-1FhSpecifiestheminimumnumberofDDR_CLKcyclesbetweentransitionsontheDDR_CKEpin,minus1.

Correspondstothet

cke

ACtimingparameterintheDDR2datasheet.Calculateby:

T_CKE=t

cke

-1

46DDR2MemoryControllerSPRU986B–November2007

SubmitDocumentationFeedback